Faculty of Engineering & Technology Electrical & Computer Engineering Department

# DIGITAL ELECTRONICS AND COMPUTER ORGANIZATION LABORATORY - ENCS2110

### Report #5

### **Introduction to QUARTUS II Software**

### Prepared by:

Obada Tahayna 1191319

Instructor: Dr. Adnan Yahya

Assistant: Eng. Katy Sadi

**Section:** 5

**Date:** 27/10/2020

### **Abstract**

The aim of the experiment is to use the QUARTUS II software to code in Verilog HDL and simulate the implemented circuit. In addition of the block diagram and turning the code into FPGA and test it .

# **Contents**

| Abstract               |    |

|------------------------|----|

| Theory                 | 3  |

| I. Quartus II Software | 3  |

| II. Verilog HDL        | 3  |

| Procedure              |    |

| I. fullAdder           | 4  |

| II. fourBitFullAdder   |    |

| III. fourBitComparator | 6  |

| IV. twoByOneMux        | 7  |

| V. The Complete System | 8  |

| Conclusion             | 10 |

| References             | 11 |

### **Theory**

#### I. Quartus II Software

The Altera Quartus II design software provides a complete multiplatform design environment that easily adapts to your specific design needs. it's a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes solutions for all phases of FPGA and CPLD design.[1]

#### II. Verilog HDL

Verilog is a hardware description language (HDL) used to model electronic systems, it's most commonly used in the design and verification of digital circuits at the register transfer level of abstraction [2]. A Verilog can be used in Quartus II by creating a Verilog file. And a module can be described in any one (or a combination) of the following modeling techniques:

- **Gate-Level Modeling:** using instantiation of primitive gate and user defined modules.

- **Data-Flow Modeling:** using continues assignment statements with keyword assign.

- **Behavioral Modeling:** using procedural assignment statements with keyword always.

### **Procedure**

In this experiment, a 4-bit full adder was constructed using 1-bit full adders then the comparator was created and the system was connected via 2x1 Mux.

#### I. fullAdder

The module was set up structurally as follows:

```

module fullAdder(a, b, cIn, sum, cOut);

2

3

input a, b, cIn;

output reg sum, cOut;

4

5

6

always @(a, b, cIn)

8

begin

\{cOut, sum\} = a + b + cIn;

9

10

end

11

endmodule

12

```

Figure 1: fullAdder Code

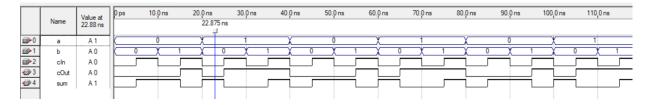

After simulating the module, the output came out as follows:

Figure 2: fullAdder Simulation

#### II. fourBitFullAdder

The 4-bit full adder was created by implementing four 1-bit full adder modules

```

=module fourBitFullAdder(a, b, cIn, sum);

1

2

3

input [3:0] a, b;

input cIn;

4

5

output [4:0] sum;

6

7

wire w1, w2, w3;

8

9

fullAdder f1(a[0], b[0], cIn, sum[0], w1);

fullAdder f2(a[1], b[1], w1, sum[1], w2);

10

fullAdder f3(a[2], b[2], w2, sum[2], w3);

11

fullAdder f4(a[3], b[3], w3, sum[3], sum[4]);

12

13

14

endmodule

```

Figure 3: fourBitFullAdder Code

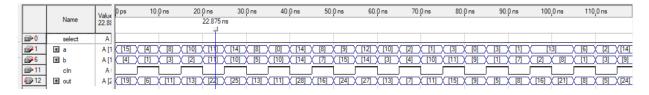

After simulating the module, the output came out as follows:

Figure 4: fourBitFullAdder Simulation

### III. fourBitComparator

The code was written behaviorally to compare between two inputs, if the first input was greater then the output will be 100, if both inputs were equal then the output will be 010, else the output will be 001.

```

module fourBitComparator(a, b, result);

1

2

3

input [3:0] a, b;

4

output reg [2:0] result;

5

6

always @(a, b)

7

begin

8

9

if(a>b)

10

begin

11

result = 3'bl00;

12

end

13

14

15

else if(a==b)

begin

16

17

result = 3'b010;

18

end

19

20

21

else if(a<b)

22

begin

23

result = 3'b001;

24

end

25

26

end

endmodule

27

```

Figure 5: fourBitComparator Code

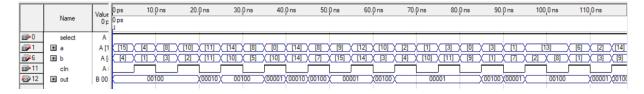

After simulating the code, results came as shown below.

Figure 6: fourBitComparator Simulation

### IV. twoByOneMux

The code was built behaviorally to choose between the two functions, if the selection input was 0 then the output will be the first option, else it will be the second one.

```

■module twoByOneMux(d0, d1, sel, result);

1

2

3

input [4:0] d0;

4

input [2:0] d1;

5

input sel;

output reg [4:0] result;

6

7

8

always @(d0, d1)

9

begin

10

11

if(sel)

12

result = d1;

13

14

else

15

result = d0;

16

17

end

18

endmodule

19

```

Figure 7: twoByOneMux Code

The figure below explains the output of the module.

Figure 8: twoByOneMux Simulation

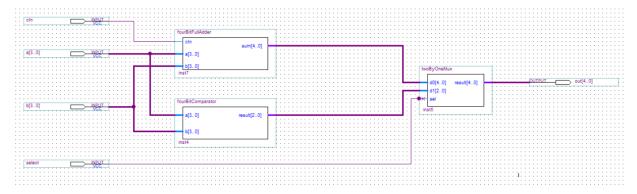

#### V. The Complete System

The System contains inputs, which are two 4-bit inputs, initial carry and the selection. The operation is executed depending on the selection input (adding or comparing), and outputs which are a 4-bit output and the final carry.

```

module project(a, b, cIn, select, out);

2

3

input [3:0] a, b;

4

input cIn, select;

output [4:0] out;

5

6

7

wire [4:0]

8

wire [2:0] w2;

9

10

11

fourBitFullAdder(a, b, cIn, w1);

12

fourBitComparator(a, b, w2);

13

14

twoByOneMux(w1, w2, select, out);

15

endmodule

16

```

Figure 9: The Complete System Code

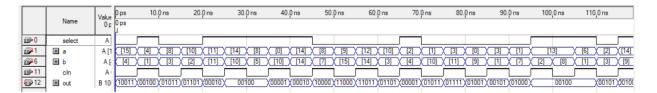

If selection equals 0, adding will be initiated. Other than that, comparing will be initiated as explained below.

Figure 10: The System Simulation - Select=0 (Adding)

Figure 11: The System Simulation - Select=0 (Comparing)

Figure 12: The System Simulation - Both Selections (Randomly)

After setting all the three modules, we created a block diagram and assigned the pins to convert the design into FPGA. the block diagram:

Figure 13: The System Schematic

### **Conclusion**

Verilog HDL and FPGA are useful ways to implements designs easily and to avoid the gates complexity. Using these methods will give you the ability to implement complex designs just by defining the functionality of the design and without the gate level complexity. Also, it gives you the ability to simulate and test the design before implementing it on the hardware.

# References

- [1]: Introduction to the Quartus II software design Book Page 2.

- [2]: https://en.wikipedia.org/wiki/Verilog Accessed on 26-10-2020 at 10:23pm