## Faculty of Engineering and Technology **Electrical and Computer Engineering Department**

**ENCS533-Advanced Digital Design**

Second Semester 2018/2019 **Duration: 120 minutes**

**Final Exam**

Instructor: Dr. Abdellatif S. Abu-Issa

Q1) (21 points)

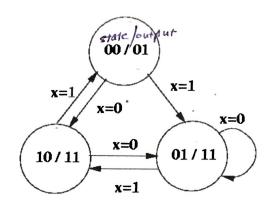

a) For the following state diagram:

i) Is this Mealy or Moore Machine and Why? [2 points]

- ii) Write a VHDL behavioural code to describe the circuit presented by the state diagram. [12 points]

- b) Show the detailed diagram for the 4-bit LUT for F =

A'B+C'D+AD'. [7 points]

Q2) (21 points)

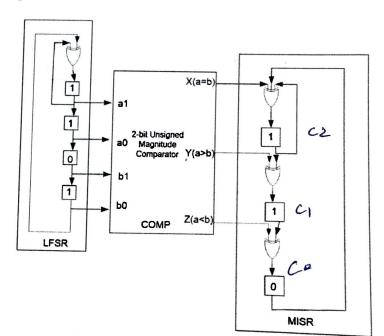

The following figure shows a Built-In Self-Test Circuit for a 2-bit magnitude comparator. The test vectors are generated using a 4-bit LFSR and the results are analysed using a 3-bit MISR as shown in the figure.

- a) Show the first 8 test vectors generated by the LFSR. The first vector of the LFSR is "1101", you should show the next 7 test vectors. [6 points]

- b) What is the fault free signature of this system after we apply these test vectors? (Initial value of the MISR "110") [9 points]

- c) Assume that the output Z(a < B) is Sa0. What is the signature after we apply the same test vectors generated by the LFSR? (Initial value of MISR is "110") [6 points] 110

Q3) (38 points)

a) Assign output values to the don't care states in the following flow table in such a way as to avoid transient output pulses. [4 points]

|   | 00   | 01       | 11    | 10           |

|---|------|----------|-------|--------------|

| а | a),0 | b,-      | -,-   | <b>d</b> , - |

| b | a,-  | (b, 1    | (b) 1 | c,*          |

| С | b,-  | ×<br>-,- | b,-   | (c,) 0       |

| d | c,-  | d, 1     | c,-   | (d, 1        |

b) An asynchronous circuit with two inputs (x1 and x2) and one output (z). When both inputs are zeros (i.e. x1 = x2 = 0) then z = 0, and when both inputs are ones (i.e. x1 = x2 = 1) then z = 1, otherwise the output will not change. Show the primitive follow table of this circuit.

[10 points]

c) Given the following primitive flow table, draw the reduced flow table after reducing the number of states. [12 points]

| 0,0 f,                             |                                    | 1,2  |

|------------------------------------|------------------------------------|------|

| 2, -3- [, -e, [<br>-2] (-) F, 1 4- | 12 @/o @/o b/o                     | 4,5  |

|                                    | 2,3 alo 6/0 010<br>1,6 600 blo d1- | ell- |

|                                    | 45 a/- b/- a/1                     | dy   |

|   |     | • 4  |          |       |             |  |  |  |

|---|-----|------|----------|-------|-------------|--|--|--|

|   | 00  | 0    | <u>l</u> | 11    | 10          |  |  |  |

| 1 | 000 | 0 2/ | 0        | -/-   | 6/0         |  |  |  |

| 2 | 170 | 2/   | 0 3      | 3/0   | -/-         |  |  |  |

| 3 | -1- | 2/,  | 0 (3     | 0 /(0 | 4/-         |  |  |  |

| 4 | 1/- | -/-  | 5        | /1    | <b>4</b> /1 |  |  |  |

| 5 | -/- | 2/-  | (3)      | V I   | 4/1         |  |  |  |

| 6 | 1/0 | -/-  | 5        | /-    | <b>⑥/ 0</b> |  |  |  |

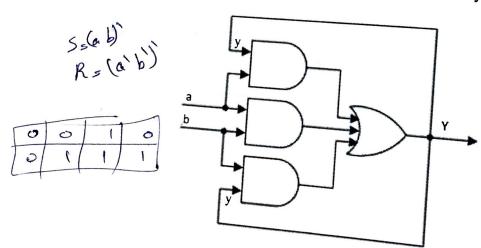

d) i) Show the transition table for the following circuit. [3 points]

ii) Implement the same circuit using SR-latch. Use NAND gates only in your design. [9 points]

© Good Luck ©