1. Need to understand and solve all HW questions

Area will be covered in Midetrm:

- Semiconductor material: pn-junction, NMOS, PMOS

- IC Manufacturing Process

- Design Metrics CMOS

- Transistor Devices

- The CMOS inverter

- Combinational logic structures

- Layout design rules

- basic gates

- Static & Dynamic CMOS Logic

- 2. What are the main design matrices?

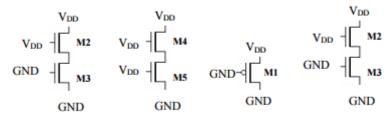

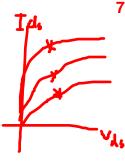

- 3. Determine the region of operation (Cut off, Linear, Saturation, ..) in the following configurations.

## See slides for detail answer

Ans: The three modes are: : The three modes are: (a) Accumulation mode when Accumulation mode when Vgs is much less than is much less than Vt (b) Depletion Depletion mode when mode when Vgs is equal to is equal to Vt (c) Inversion Inversion mode when mode when Vgs is greater than Vt

4. What are the three regions of operation of a MOS transistor?

Ans: The three regions are: : The three regions are: Cut-off region: This is essentially the accumulation mode, where there is no effective flow of current between the source and drain. Non-saturated region saturated region: This is the active, active, linear or week inversion region, where the drain current is dependent on both the gate and Ajit Pal, IIT Kharagpur drain voltages. Saturated region: This is the strong inversion region, where the drain current is independent of the drain drain current is independent of the drain-to-source voltage but urce voltage but depends on the gate voltage.

5. Determine the region of operation (Cut off, Linear, Saturation, Vel. saturation) in the following configurations. You may assume that all transistors have identical sizes. VDD = 2.5V. Explain your reasoning, and show your derivations if needed.

•

$$V_{DD} V_{GS} = V_{DS} = V_{DD}$$

$$V_{DD} V_{DS} = V_{DS} = V_{DS}$$

$$V_{DD} V$$

- 6. How does Increasing W of devices affect it's resistance, Gate capacitance and transconductance?

- decreases the resistance; allows more current to flow A resistor:  $R_{\rm n} = \frac{1}{\mu_{\rm n} C_{\rm ox}(V_{\rm GS}-V_{\rm Tn})} \left(\frac{L}{W}\right)$  (among other things ...) Increasing W decreases the resistance; allows more current to flow

Oxide capacitance  $C_{\rm ox} = \varepsilon_{\rm ox}/t_{\rm ox}$  [F/cm²]

Transconductance

$$|\beta_n| = \mu_n C_{ox} \left(\frac{W}{L}\right) = k'_n \left(\frac{W}{L}\right)$$

Gate capacitance  $C_G = C_{ox} \underbrace{WL}_{Area}$  [F]

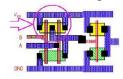

**7.** What is transconductance of a MOS transistor? Explain its role in the operation of the transistor.

Ans: Trans-conductance is represented by the change in drain current for change in gate voltage for constant value of drain voltage. This parameter is somewhat similar to  $\beta$ , the current gain of bipolar junction transistors. The Answer to the Questions of Lec Answer to the Questions of Lec-4 Ajit Pal, IIT Kharagpur the current gain of bipolar junction transistors. The following equation shows the dependence of on various parameters. As MOS transistors are voltage controlled devices, this parameter plays an important role in identifying the efficiency of the MOS transistor.

9. Explain the behaviour of a pMOS transistor as a switch.

10. How one nMOS and one pMOS transistor are combined to behave like an ideal switch.

11. The input of a lightly loaded transmission gate is slowly changes from HIGH level to LOW level. How the currents through the two transistors vary?

12. How its ON-resistance of a transmission gate changes as the input varies from 0 V to Vdd, when the output has a light capacitive load.

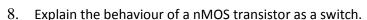

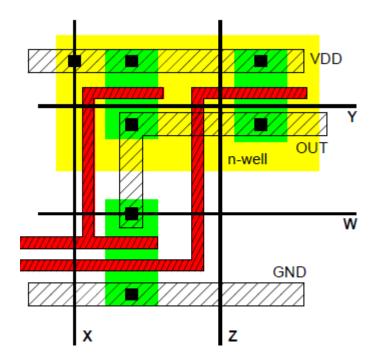

13. Draw stick digral/layout for 2-INPUT AND?

14. Mark or point to the active, via/contact, M1, poly, NWELL IN THE FIGURE BELOW

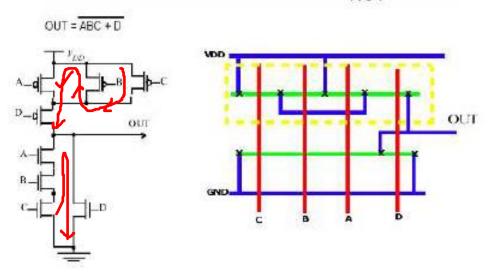

15. Draw schematic and stick diagram for Out= (ABC+D)'

**16.** What is the difference between Average, maximum and instantious power? **See slide notes for answer**

17. Q4. Why leakage power dissipation has become an important issue in deep submicron technology? What are the main factors that affects leakage?

# See slide notes for answer

Ans: In deep submicron technology deep submicron technology the leakage component the leakage component becomes a significant percentage of the total power and the leakage current increases at a

faster rate than dynamic power amic power in new technology generations. That is why the leakage pow generations. That is why the leakage power has become an important issue.

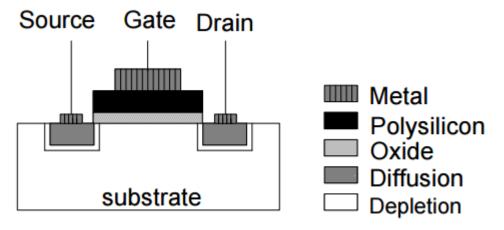

18. Show the basic structure of a MOS transistor.

Ans: The basic structure of a MOS transistor is given below. On a lightly doped substrate of silicon two islands of diffusion regions called as source and drain, of opposite polarity of that of the substrate, are created. Between these two regions, a thin insulating layer of silicon dioxide is formed and on top of this a conducting material made of poly-silicon or metal called gate is deposited.

19. What are the commonly used conducting layers used in IC fabrication?

Ans: Fabrication involves fabrication of Fabrication involves fabrication of patterned laye atterned layers of the rs of the three conducting materials: metal, poly-silicon silicon and diffusion by using a series of photolithographic techniques and chemical processes involving oxidation of silicon, diffusion of impurities into the silicon and deposition and etching of aluminum or Ajit Pal, IIT Kharagpur polysilicon polysilicon on the silicon to provide interconnection

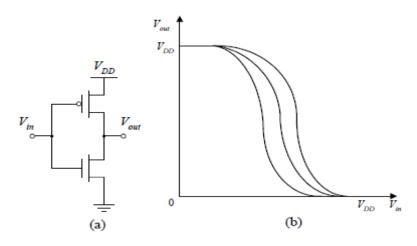

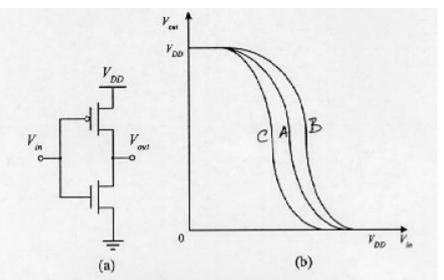

20. Consider the CMOS inverter from below. If the NMOS transistor has channel width Wn and the PMOS transistor has channel width, Wp, label the voltage transfer characteristics from FIG. 2.b that correspond to following device sizes:

A:  $W_n = 5 \mu m$ ,  $W_p = 5 \mu m$

B:  $W_n = 1 \mu m$ ,  $W_p = 5 \mu m$

C:  $W_n = 5 \mu m$ ,  $W_p = 1 \mu m$

Maximusum, symmetrical margins =>  $V_{m} = \frac{V_{oH} + V_{oL}}{2}$   $V_{m} = IV$   $\frac{W_{p2}}{W_{p2}} = \frac{V_{n}}{K_p'} \frac{V_{DSATm} \left(V_{M} - V_{Tm} - V_{DSATm}/2\right)}{K_p'} = \frac{V_{obs}}{V_{DSATp}} \left(\frac{V_{DS}}{V_{M}} + V_{Tp} + V_{DSATp}/2\right) = \frac{V_{obs}}{V_{obs}} \frac{V_{obs}}{V_{obs}} = \frac{115\mu}{30\mu} \frac{0.6}{1} \frac{0.3}{0.6} = 1.15$  $W_{p2} = W_{m2} \times 1.15 = 5.75\mu m$

21. A CMOS inverter with supply voltage VDD1 = 2V, has to interface to a second CMOS inverter with VDD2 = 2.5V supply, as shown below

The transistor widths of the second inverter  $W_{n2}$ ,  $W_{p2}$ , should be determined to assure reliable interfacing, since the high output voltage level of the first inverter is  $VOH_1 = 2V$ . If  $W_{n2} = 5\mu m$ , determine the value of  $W_{p2}$ , such that these inverters are interfaced with maximum and symmetrical noise margins.

$$V_{DD1} = 2V \qquad V_{DD2} = 2.5V$$

$$V_{out1} \qquad W_{n2,Wp2}$$

$$V_{out2} \qquad V_{out2}$$

Maximuzur, symmetrical margins =>

$$V_{m} = \frac{V_{out} + V_{out}}{2}$$

$V_{m} = IV$

$\frac{W_{p2}}{W_{p2}} = \frac{V_{n}}{V_{p}} \frac{V_{DSATm} \left(V_{M} - V_{Tm} - V_{DSATm}/2\right)}{V_{p}} = \frac{V_{out}}{V_{p}} \frac{V_{DSATp}}{V_{p}} \left(\frac{V_{p}}{V_{p}} + \frac{V_{p}}{V_{p}} + \frac{V_{DSATp}}{V_{p}}\right) = \frac{V_{out}}{V_{p}} \frac{V_{out}}{V_{p}} \left(\frac{V_{p}}{V_{p}} + \frac{V_{p}}{V_{p}} + \frac{V_{DSATp}}{V_{p}}\right) = \frac{V_{out}}{V_{p}} \frac{V_{p}}{V_{p}} = \frac{V_{p}}{V_{p}} \times 1.15 = 5.75 \mu m$

$W_{p2} = 5.75 \mu m$

22. The inverter from FIG. below . has Wn = 1 mm and Wp = 2.5mm. VDD = 2.5V. Determine the value of VOH. Assume that the PMOS transistor operates in triode region and

$$\left| \frac{V_{DS}}{2} \right| \ll \left| V_{GS} - V_T \right|$$

, Determine VoH also the value of  $VOL$ .

$$V_{in}$$

$V_{out}$

$R=10k\Omega$

$\begin{aligned}

& \overline{L_{P}} = \overline{L_{P}} = \overline{L_{P}} \left[ (V_{GS} - V_{P}) V_{DS} - \frac{V_{DS}}{2} \right] \approx \underbrace{FIG.4 \, CMOS \, inverter \, with \, resistive \, load} \\

& \approx \overline{L_{P}} \left( V_{GS} - V_{P} \right) V_{DS} ; \quad V_{DS} = V_{OH} - V_{DD} \\

& V_{OH} = R \cdot \overline{L_{D}} = R \cdot \overline{L_{P}} \cdot \left( V_{GS} - V_{P} \right) \cdot \left( V_{OD} + V_{OH} \right) \\

& V_{OH} = \frac{R \, \overline{L_{P}} \left( V_{GS} - V_{P} \right) \, V_{DD}}{1 - R \, \overline{L_{P}} \left( V_{GS} - V_{P} \right)} = 2.16 \, V

\end{aligned}$   $\begin{aligned}

& V_{OL} = OV : P_{MOS} \text{ is OFF} \end{aligned}$

$$\mathbf{v}_{OH} = 2.16 V$$

$\mathbf{v}_{OL} = 0 V$

# FORMULAS AND EQUATIONS

#### Diode

$$\begin{split} I_D &= I_S(e^{V_D/\phi_T} - 1) = Q_D/\tau_T \\ C_j &= \frac{C_{j0}}{(1 - V_D/\phi_0)^m} \\ K_{eq} &= \frac{-\phi_0^m}{(V_{high} - V_{low})(1 - m)} \times \\ & [(\phi_0 - V_{high})^{1 - m} - (\phi_0 - V_{low})^{1 - m}] \end{split}$$

## **MOS Transistor**

$$\begin{split} V_T &= V_{T0} + \gamma (\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|}) \\ I_D &= \frac{k'_n W}{2 L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \text{ (sat)} \\ I_D &= \upsilon_{sat} C_{ox} W \bigg( V_{GS} - V_T - \frac{V_{DSAT}}{2} \bigg) (1 + \lambda V_{DS}) \\ & \text{ (velocity sat)} \\ I_D &= k'_n \frac{W}{L} \bigg( (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \bigg) \text{ (triode)} \\ I_D &= I_S e^{\frac{V_{GS}}{nkT/q}} \bigg( 1 - e^{-\frac{V_{DS}}{kT/q}} \bigg) \text{ (subthreshold)} \end{split}$$

### **Deep Submicron MOS Unified Model**

$$\begin{split} I_D &= 0 \text{ for } V_{GT} \leq 0 \\ I_D &= k' \frac{W}{L} \bigg( V_{GT} V_{min} - \frac{V_{min}^2}{2} \bigg) (1 + \lambda V_{DS}) \text{ for } V_{GT} \geq 0 \\ \text{with } V_{min} &= \min(V_{GT}, V_{DS}, V_{DSAT}) \\ \text{and } V_{GT} &= V_{GS} - V_T \end{split}$$

## **MOS Switch Model**

$$\begin{split} R_{eq} &= \frac{1}{2} \bigg( \frac{V_{DD}}{I_{DSAT} (1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DSAT} (1 + \lambda V_{DD}/2)} \bigg) \\ &\approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \bigg( 1 - \frac{5}{6} \lambda V_{DD} \bigg) \end{split}$$

#### Inverter

$$\begin{split} V_{OH} &= f(V_{OL}) \\ V_{OL} &= f(V_{OH}) \\ V_{M} &= f(V_{M}) \\ t_{p} &= 0.69 R_{eq} C_{L} = \frac{C_{L}(V_{swing}/2)}{I_{avg}} \\ P_{dyn} &= C_{L} V_{DD} V_{swing} f \\ P_{stat} &= V_{DD} I_{DD} \end{split}$$

# **Static CMOS Inverter**

$$V_{OH} = V_{DD}$$

$$V_{OL} = GND$$

$$V_{M} \approx \frac{rV_{DD}}{1+r} \quad \text{with} \quad r = \frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}}$$

$$V_{IH} = V_{M} - \frac{V_{M}}{g} \qquad V_{IL} = V_{M} + \frac{V_{DD} - V_{M}}{g}$$

$$\text{with } g \approx \frac{1+r}{(V_{M} - V_{Tn} - V_{DSATn}/2)(\lambda_{n} - \lambda_{p})}$$

$$t_{p} = \frac{t_{pHL} + t_{pLH}}{2} = 0.69C_{L}\left(\frac{R_{eqn} + R_{eqp}}{2}\right)$$

$$P_{av} = C_{L}V_{DD}^{2}f$$

#### Interconnect

Lumped RC:  $t_p = 0.69 RC$ Distributed RC:  $t_p = 0.38 RC$ RC-chain:

$$\tau_N = \sum_{i=1}^N R_i \sum_{j=i}^N C_j = \sum_{i=1}^N C_i \sum_{j=1}^i R_j$$

Transmission line reflection: ',

$$\rho = \frac{V_{refl}}{V_{inc}} = \frac{I_{refl}}{I_{inc}} = \frac{R - Z_0}{R + Z_o}$$