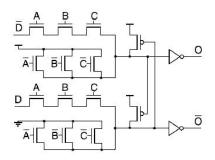

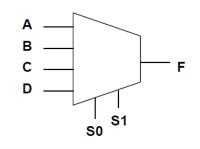

### 1. What is the logic function of the following gate?

O=ABCD

## FORMULAS AND EQUATIONS

· •

Diode

$$I_{D} = I_{S}(e^{V_{D}/\phi_{T}} - 1) = Q_{D}/\tau_{T}$$

$$C_{j} = \frac{C_{j0}}{(1 - V_{D}/\phi_{0})^{m}}$$

$$K_{eq} = \frac{-\phi_{0}^{m}}{(V_{high} - V_{low})(1 - m)} \times [(\phi_{0} - V_{high})^{1 - m} - (\phi_{0} - V_{low})^{1 - m}]$$

#### **MOS Transistor**

$$V_T = V_{T0} + \gamma (\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|})$$

$$I_D = \frac{k'_n W}{2 L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \text{ (sat)}$$

$$I_D = v_{sat} C_{ox} W \left( V_{GS} - V_T - \frac{V_{DSAT}}{2} \right) (1 + \lambda V_{DS}) \text{ (velocity sat)}$$

$$I_{D} = k_{n}' \frac{W}{L} \left( (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right) \text{ (triode)}$$

$$I_{D} = I_{S} e^{\frac{V_{GS}}{nkT/q}} \left( 1 - e^{-\frac{V_{DS}}{kT/q}} \right) \text{ (subthreshold)}$$

#### **Deep Submicron MOS Unified Model**

$$\begin{split} I_D &= 0 \text{ for } V_{GT} \leq 0 \\ I_D &= k' \frac{W}{L} \left( V_{GT} V_{min} - \frac{V_{min}^2}{2} \right) (1 + \lambda V_{DS}) \text{ for } V_{GT} \geq 0 \\ \text{with } V_{min} &= \min(V_{GT}, V_{DS}, V_{DSAT}) \\ \text{and } V_{GT} &= V_{GS} - V_T \end{split}$$

#### **MOS Switch Model**

L

$$R_{eq} = \frac{1}{2} \left( \frac{V_{DD}}{I_{DSAT}(1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DSAT}(1 + \lambda V_{DD}/2)} \right)$$

$$\approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left( 1 - \frac{5}{6} \lambda V_{DD} \right)$$

#### Inverter

$$V_{OH} = f(V_{OL})$$

$$V_{OL} = f(V_{OH})$$

$$V_{M} = f(V_{M})$$

$$t_{p} = 0.69R_{eq}C_{L} = \frac{C_{L}(V_{swing}/2)}{I_{avg}}$$

$$P_{dyn} = C_{L}V_{DD}V_{swing}f$$

$$P_{stat} = V_{DD}I_{DD}$$

#### Static CMOS Inverter

$$V_{OH} = V_{DD}$$

$$V_{OL} = GND$$

$$V_{M} \approx \frac{rV_{DD}}{1+r} \quad \text{with} \quad r = \frac{k_p V_{DSATp}}{k_n V_{DSATn}}$$

$$V_{IH} = V_M - \frac{V_M}{g} \qquad V_{IL} = V_M + \frac{V_{DD} - V_M}{g}$$

with  $g \approx \frac{1+r}{(V_M - V_{Tn} - V_{DSATn}/2)(\lambda_n - \lambda_p)}$

$$t_p = \frac{t_{pHL} + t_{pLH}}{2} = 0.69 C_L \left(\frac{R_{eqn} + R_{eqp}}{2}\right)$$

$$P_{av} = C_L V_{DD}^2 f$$

#### Interconnect

Lumped RC:  $t_p = 0.69 RC$ Distributed RC:  $t_p = 0.38 RC$ : RC-chain:

$$\tau_{N} = \sum_{i=1}^{N} R_{i} \sum_{j=i}^{N} C_{j} = \sum_{i=1}^{N} C_{i} \sum_{j=1}^{i} R_{j}$$

Transmission line reflection:

$$\rho = \frac{V_{refl}}{V_{inc}} = \frac{I_{refl}}{I_{inc}} = \frac{R - Z_0}{R + Z_o}$$

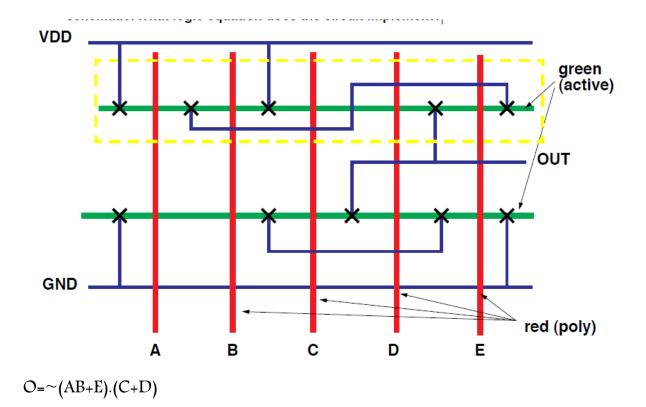

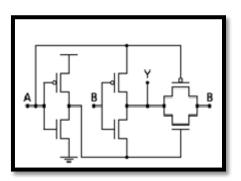

2. Consider the following stick diagram. Draw the electrically equivalent transistor-level Schematic. What logic equation does the circuit implement?

#### 3. Consider the logical expression

out=  $\sim$ ((a+b) • (c+d))

. Convert this to a schematic diagram for static CMOS logic, then convert it to a stick-diagram layout (as in question 1).

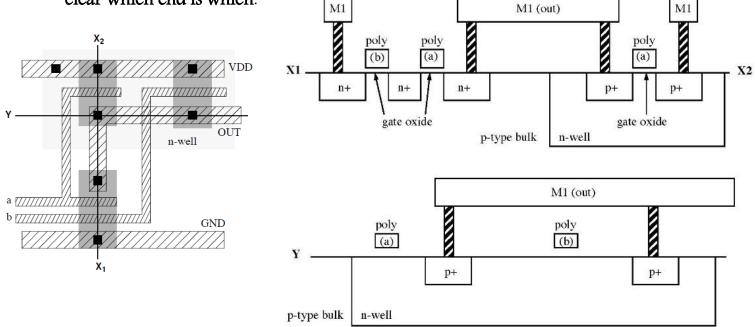

4. Provide a side-view diagram for each of the cuts X and Y through the layout below. Be sure to label each of the strata. Label your endpoints for the X cut, so it is (vdd) clear which end is which.

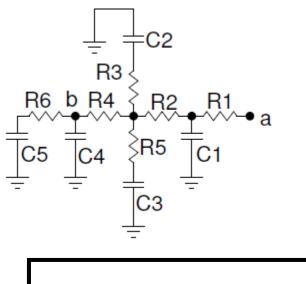

5. Determine the Elmore delay from Node a to Node b in the following circuit.

$\tau_{ab} = R1(C1 + C2 + C3 + C4 + C5) + R2(C2 + C3 + C4 + C5) + R4(C4 + C5)$

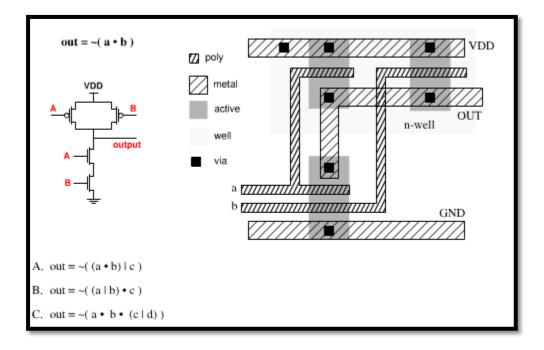

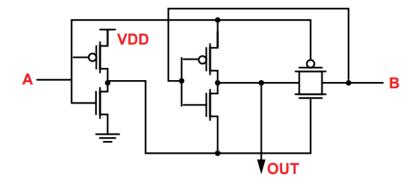

6. What is the output function of the following circuit?

XOR

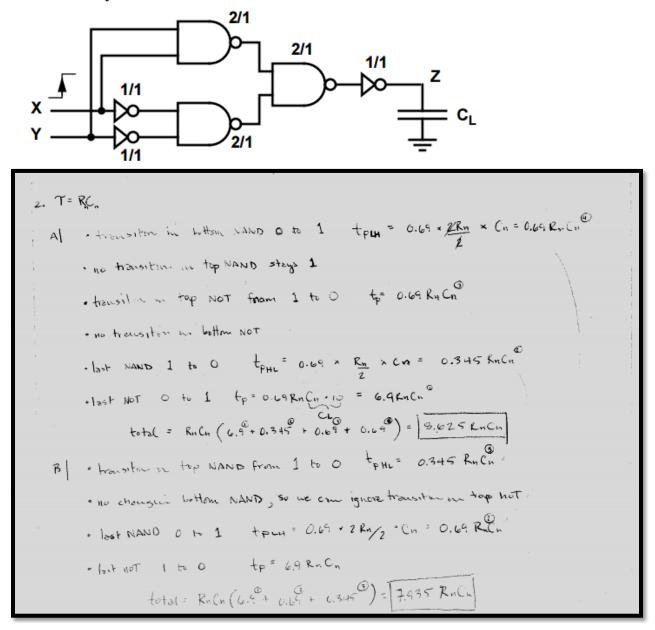

7. Consider the CMOS circuit shown below In the figure, the W/L ratios for each gate apply to both NMOS and PMOS transistors. We want to determine the delay from a rising transition  $(0 \rightarrow 1)$  .....

A. Assuming that the rise and fall times are good approximations of the propagation delay, determine the delay from X to Z, in terms of  $\tau$ , when Y = 0. B. Now, assume that Y = 1. What is the new value for the propagation delay from X to Z? Can you comment on this?

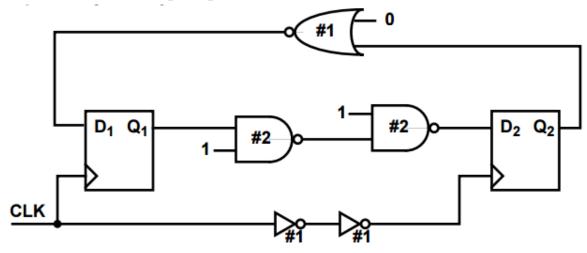

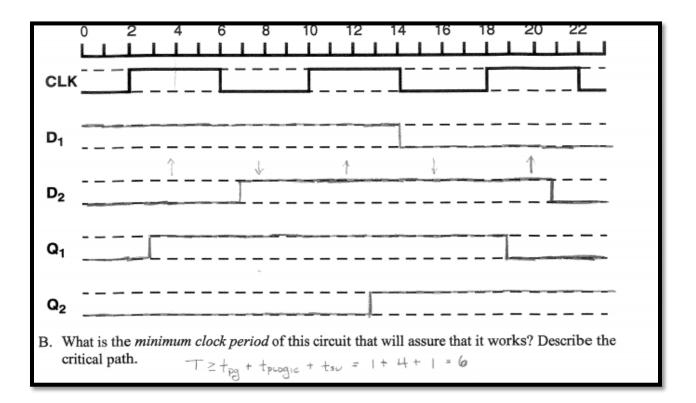

8. The circuit shown below uses two identical rising edge triggered Flip-Flops. Assume that for both Flip-Flops, .....

A.Complete the following timing diagram for the circuit. Assume the initial states of Q1 and Q2 are 0, and have remained at 0 for a long time (but no clock edge has come along yet to latch the 1 value at D1).

B. What is the minimum clock period of this circuit that will assure that it works? Describe the critical path.

#### Above

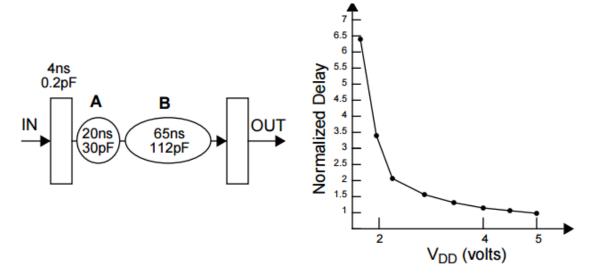

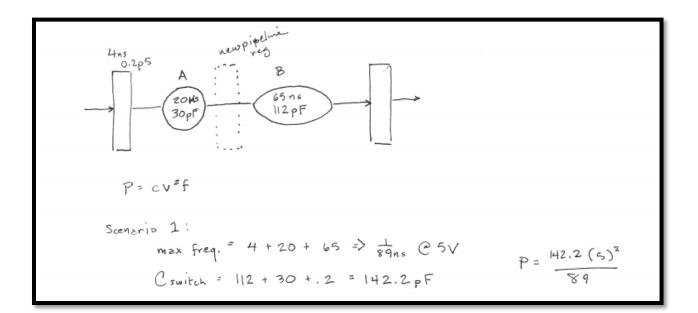

9. Consider the circuit below, left. Modules A and B have a delay of 20nsec and 65nsec at 5V and switch 30pF and 112pF, .....

Scenario 2:

$$M \gg x$$

freq. = 4 + 65 =>  $\frac{1}{69} + 2.5V$  but we will still be

$V \approx 60\%$  so to be the equal to the manning C  $\frac{1}{59} + 3.5$ , so to be the equal to the second of the equal to the second of the equal to the second of the equal to the e

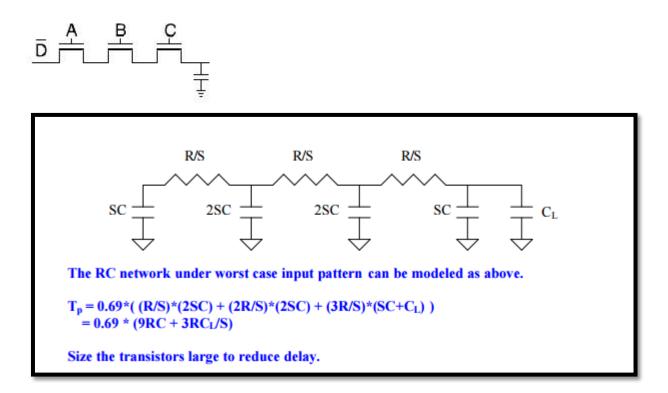

10. The serial NMOS transistors in the logic section of the CPL gate shown below are clearly on the critical path. We have extracted that critical path in the figure shown below. .....

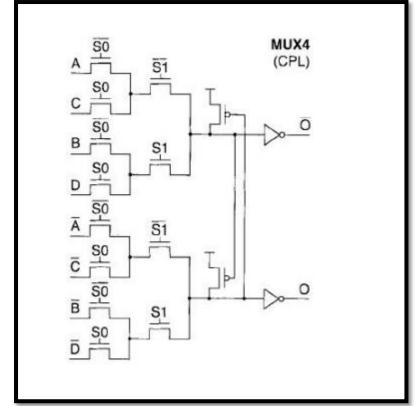

11. Design a 4 input multiplexer (see the truth-table below for its fuction) in the complementary pass-transistor logic style using a minimum number of transistors.

| S0 | S1 | Output |

|----|----|--------|

| 0  | 0  | А      |

| 0  | 1  | В      |

| 1  | 0  | С      |

| 1  | 1  | D      |

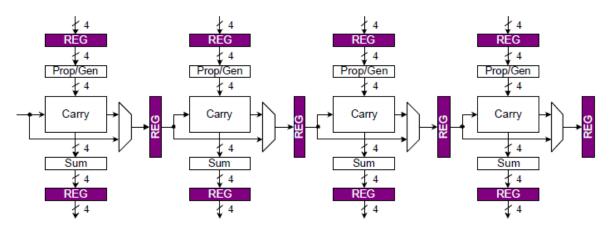

1) You have a carry-bypass adder with 4 bits per stage but you find that it is too slow

for large total number of bits. Being lazy to go for a different design, you pipeline the

adder. A 12-bit section of your circuit is shown in Fig. 4. Answer the questions (a)-(b)

in terms of the total number of bits, N, and the following one-bit delays:

tppg delay through the propagate/generate block = 0.6ns

tpcarry delay of a single carry bit = 1ns

tpsum delay of a single sum bit = 2ns

tpmux delay of the multiplexer = 0.4ns

tpreg delay of the register = 0.5ns

a) (4 pts) What is the minimum clock period you can use for your N-bit adder? (i.e.

The worst-case scenario occurs in the first block, where input carry is not available and needs to be generated.

The worst-case carry propagation delay is: tp(carry) = tp<sub>reg</sub> + tp<sub>pg</sub> + 4tp<sub>carry</sub> + tp<sub>mux</sub> = 5.5ns

The worst-case sum propagation delay is: tp(sum) = tp<sub>reg</sub> + tp<sub>pg</sub> + 3tp<sub>carry</sub> + tp<sub>sum</sub> = 6.1ns

The minimum clock period is therefore: T<sub>Clk</sub><sup>min</sup> = max {tp(carry), tp(sum)} = 6.1ns

The clock period does not depend on the number of bits

b) (3 pts) How many clock cycles does it take for the first N-bit addition to complete?

```

There are total of B_{tot} = (N/4 - 1) blocks needed for an N-bit addition. Each block computes with inputs of the preceding blocks. Therefore, it takes N/4 - 1 clock cycles to complete N-bit addition.

```

The latency is linearly dependent on the number of bits.

**11.16** Consider a ring oscillator consisting of five inverters, each having  $t_{PLH} = 60$  ns and  $t_{PHL} = 40$  ns. Sketch one of the output waveforms, and specify its frequency and the percentage of the cycle during which the output is high.

А tpin=60ns В tpHI = 40ns С 60 40 D 60 F When output is high,  $\rightarrow$ н 60ns + 40ns + 60ns + 40ns + 60ns = 260ns When output is low, 60ns + 40ns + HOns 60ns + 40ns = 240ns Period = (240ns + 260ns) = 500nsFrequency = Period = 2MHz To of cycle for which the output is high  $\frac{260ns}{500ns} = .52$  or  $\frac{52\%}{52\%}$

# **11.17** A ring-of-eleven oscillator is found to oscillate at 20 MHz. Find the propagation delay of the inverter.

For 11 inverters, there are 2(11) = 22 transitions whose average length is  $t_p = \int \frac{1}{20 \times 10^6} \left( \frac{1}{22} \right) = 2.27 \text{ ns}$