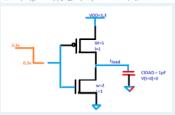

Correct Mark 5.00 out of 5.00 A step input is applied at time t=0 to the loaded inverter with dimensions and initial conditions as shown below.

For all transistors:  $L_{min}=1~\mu m,~W_{min}=1~\mu m,~V_{T,p}=-1~V,~\mu_p C_{ox}=(1/6)~x~10^{-3}~A/V^2,~\lambda_p=0.0V^{-1},~V_{T,1}=1~V,~\mu_n C_{ox}=(1/2)~x~10^{-3}~A/V^2,~\lambda_n=0.0V^{-1}.$

What region the PMOS will be in? (Linear, Cutoff, Saturation)

What region the NMOS will be in ?

What is the current load immediately after the step is applied in mA? Note: do not add a unit, just the number

## Your answer is correct.

$$\begin{split} & \text{PMDS: } V_{\text{DS}} = -3V & V_{\text{BS}} = -2\sqrt{3}V \\ & V_{\text{DS}} = V_{\text{SB}} = -2V > V_{\text{BS}} & \frac{\tau_{\text{e}} t_{\text{PMS}} t_{\text{constrained}}}{\tau_{\text{e}} t_{\text{e}} t_{\text{constrained}}} \\ & \text{NMMS: } V_{\text{DS}} = 0.0V \leq V_{\text{NA}} = 2V & \frac{\tau_{\text{e}} t_{\text{e}} t_{\text{constrained}}}{2V} \\ & \frac{\tau_{\text{e}} \tau_{\text{EA}} \tau_{\text{e}} \frac{\mu_{\text{e}}^{T} t_{\text{e}}}{2V} \left(\frac{t_{\text{e}}}{U}\right) \left(V_{\text{BC}} \tau^{-1} V_{\text{e}}\right)^{2L}}{\tau_{\text{e}}} \\ & \approx \frac{\left(V_{\text{b}} v_{\text{e}} t_{\text{e}}\right)^{2} A_{\text{e}} v_{\text{e}}^{2}}{2V} \left(\frac{\tau_{\text{e}}^{T}}{V_{\text{e}}}\right) \left(2.0V - -1V\right)^{2L}}{\tau_{\text{e}}^{T}} \\ & = \frac{\left[I_{\text{e}} G T_{\text{e}} h_{\text{e}}^{T}\right]}{2V} \left(I_{\text{e}} t_{\text{e}}^{T}\right)^{2L}} \end{split}$$

What region the PMOS will be in? (Linear, Cutoff, Saturation)  $\rightarrow$  Saturation,

What region the NMOS will be in ?  $\rightarrow$  Cutoff,

What is the current I/oad immediately after the step is applied in mA?

Note: do not add a unit, just the number  $\rightarrow 1.67$

Question 2 Partially correct Mark 0.67 out of 1.00 P Flag question

Match to the correct answer

Performance

Area

Body (substrate) normally connected to ------ for NMOS

The interface between designer and process (CMOS fabrication) engineer

used in chip manufacturing

Raising source voltage increases ----- of transistor

Directly affects cost 💠 🗶 Directly affects cost ♦ ✓ Power-Delay Product \$

Your answer is partially correct.

You have correctly selected 4. The correct answer is: Performance → Power-Delay Product,

Area → Directly affects cost,

Body (substrate) normally connected to --------- for NMOS → Threshold Voltage,

The interface between designer and process (CMOS fabrication) engineer  $\rightarrow$  Design Rules,

used in chip manufacturing  $\rightarrow$  Silicon,

Raising source voltage increases ——— of transistor  $\rightarrow$  Threshold Voltage