#### DEPARTMENT OF COMPUTER SYSTEM ENGINEERING Digital Integrated Circuits - ENCS333

#### Dr. Khader Mohammad Lecture #11

Parasitic Capacitance Estimation

# Agenda

Parasitics in Circuit Design

• Where do parasitics come from?

Parasitics Estimation

Scaling of parasitics for simulations

#### What Parasitics are Contained in a Circuit?

- Transistor related parasitics:

- Gate Capacitance

- Diffusion Capacitance

- Interconnect related parasitics:

- Interconnect Resistance and Capacitance

- Cross Capacitance (xcap)

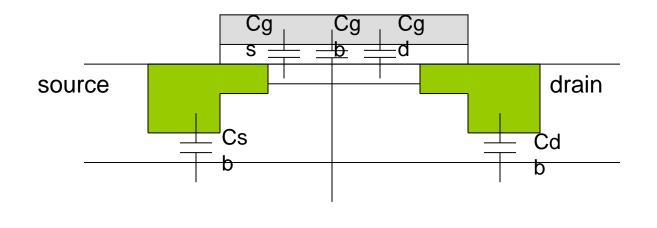

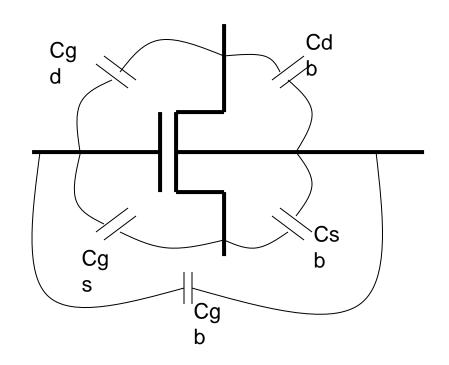

## **Transistor Parasitics**

- Cgs, Cgd are gate-to-channel capacitances

- Cgb is gate-to-bulk capacitance

- Csb, Cdb are source/drain diffusion capacitances

#### **Transistor Parasitics**

- Cgs, Cgd are gate-to-channel capacitances

- Cgb is gate-to-bulk capacitance

- Csb, Cdb are source/drain diffusion capacitances

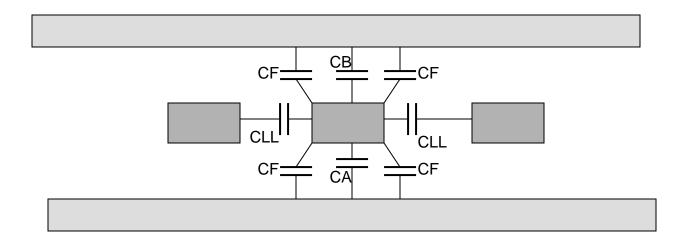

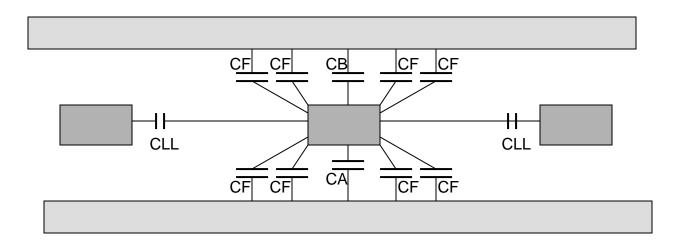

#### **Interconnect Parasitics**

- CLL Line to line Capacitance

- CA,CB Capacitance to other plane

- CF Fringing Capacitance

#### **Interconnect Parasitics**

Adding additional spacing will decrease the value of the CLL, but may cause additional fringing capacitance.

# Agenda

Parasitics in Circuit Design

• Where do parasitics come from?

Parasitics Estimation

Scaling of parasitics for simulations

## Where do Parasitics Come From

- Extraction

- Different types of extraction tools will use the layout to produce values for device and interconnect parastics.

- Estimation

- For designs that do not have layout, there are various ways of estimating parasitics.

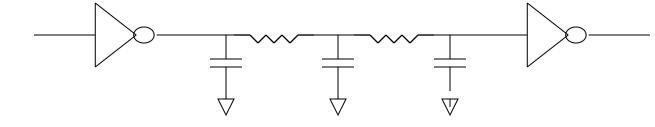

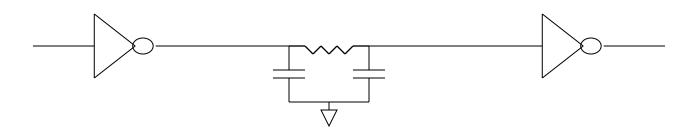

# Lumped or Distributed?

Distributed Interconnect Parasitics contain Rs and Cs

Lumped Interconnect Parasitics contain only Cs.

# **Common Parasitics File Types**

- Nets

- Distributed interconnect parasitics, resistance and capacitance

- Comes from extraction tool, and can be named for that tool (e.g. mntcl, stntcl, antcl ...)

- Device parasitics

- Device parasitics, specified in terms of area and perimeter of the devi

- Also named for the extraction tool (mdpf, adpf, stdpf, ...)

- .xcab

- Cross capacitance list

- Lists all "attackers" for each net that is a "victim"

- Can be generated from the nets file

- .RC

- Lumped interconnect parasitics, capacitance only

- Can be generated from the nets file, or estimated.

- Stitched interface

- Stitched interface and stitched netcell files.

- Generated from the .ntcl file

- Distributed interconnect

- Distributed interconnect parasitics, resistance and capacitance, used by timing tool

?

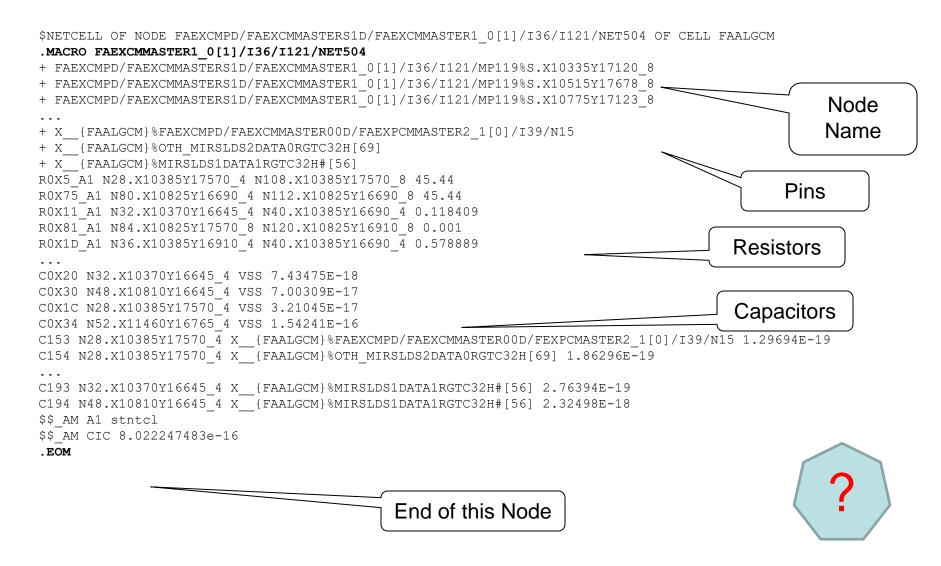

### NET File

# **DPF** File

- Lists all devices in the design

- Lists all four nodes connected to the device: drain,gate,source,bulk

- Gives values for device length and width

- Gives values for area/perimeter of drain and source

?

#### • Example:

@/i7/mp49 p vcc vcc (model=p\_i z=0.85 l=0.04 ps=1.13 as=0.119 ad=0.119 pd=1.13 cjs=6.57664e-16 cgate=7.244e-16 cjd=6.57664e-16

# **RCD** File

- Lists of all node in the design

- Has values for total cap, gate cap, interconnect cap, and cross cap.

- Interconnect cap can come from lumping of .ntcl file capacitances, or from estimation.

## **XTAB** File

- Lists each attacker of each node in the design.

- Comes adding the xcap from the .ntcl file

• Example:

BEGIN\_ENTRY /NET510 ATTR XCAP {FMEXPD}%N2 3.88583e-06 {FMEXPD}%N8 7.14513e-06 END\_ATTR END\_ENTRY

# Agenda

Parasitics in Circuit Design

• Where do parasitics come from?

Parasitics Estimation

Scaling of parasitics for simulations

# What is Parest?

- When no layout is available for extraction, we must use some tool to estimate the parasitics.

- Estimation can be done for both dynamic and static simulations.

- Estimating devices parasitics is pretty accurate.

- Size of devices is contained in the schematic.

- Estimating interconnect parasitics is <u>very</u> inaccurate.

- Length/width/metal\_layer of net is not in the schematic

# What is an FTRC, and how is it used?

- FTRC (File Tracking Resistor and Capacitors) is a schematic element used to describe the metal interconnect.

- Values are provided by the user for:

- Length

- Width

- MCF

- Spacing

- Model (Includes routed metal layer, above metal layer, and below metal layer. For example, rm3m2m4)

- FTC and FTR elements are also available.

- Information stored in the process file is used to determine the value of the Rs and Cs.

- Used for simulation schematics only, not production schematics

# Agenda

Parasitics in Circuit Design

• Where do parasitics come from?

Parasitics Estimation

Scaling of parasitics for simulations

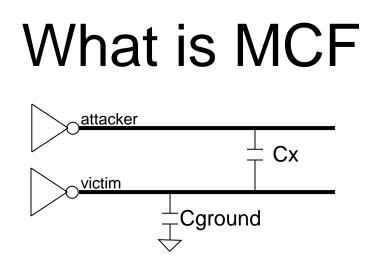

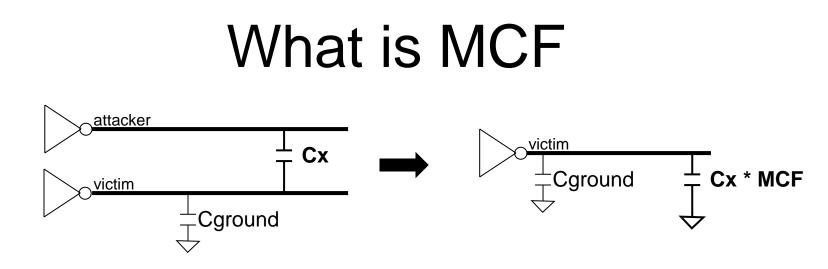

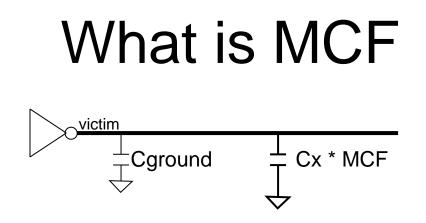

- In the figure above, the time it takes for the "victim" signal to switch can depend on the "attacker" signal.

- The attacker signal can speed up the victim signal if it is switching at the same time and in the same direction as the victim.

- The attacker signal can slow down the victim signal if it is switching at the same time and in the opposite direction as the victim.

- We can model this speed-up or slow-down of the victim timing by increasing or decreasing the value of the Capacitance on that net.

- We will multiply the Cx capacitor by some "MCF" value. (from 0 2).

- MCF is a dynamic property, but can be modeled by static timing tools.

- The cross-capacitor is de-coupled from the attacker and the value is multiplied by the "MCF" factor.

- If the attacker is slowing down the victim, an MCF value of 2.0 is applied. If the attacker is speeding up the victim, an MCF value of 0.0 is applied.

- For Tejas MCF values of 2.0/0.0 (max/min) were applied to all crosscapacitances for signals from the same bus, as they had a high chance of switching at the same time as each other.

- For other signals a backoff of the 2.0/0.0 values was given, and MCF values of 1.5/0.5 were applied.

- Note Capacitances to ground were unaffected ("Cground" in the figure above)

- Yonah/Merom do not use this methodology.

- Each Project must decide what to do about MCF modeling.

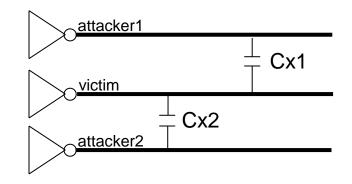

## What is "Average MCF" ?

- A victim is typically attacked by more than one other net.

- If the MCF between the "victim" and "attacker1" is 2 and the MCF between "victim" and "attacker2" is 1, we could say that the Average MCF of the victim is 1.5.

- We DO NOT use the Average MCF number in any post-layout flow.

# How are Parasitics Scaled for Timing Runs?

- Static Timing:

- Parasitics are extracted at a "typical" corner but values on the actual chips may be slightly different.

- Because timing runs both a max and min run, we have the option of scaling our "typical" parasitics to make each runs "worst-case".

- For projectx:

- In the Max run, all resistances were scaled by 1.15.

- In the Min run, capacitances were scaled by 0.80

- For projecty:

- No resistances were scaled

- In the Min run, capacitance were scaled by 0.80

- Dynamic Timing:

- FTRC devices will scale as different process corners are used. Selecting a particular corner will determine if your interconnect is modeled as "fast", "slow", or "typical".