#### Massachusetts Institute of Technology Department of Electrical Engineering and Computer Science 6.012

## Microelectronic Devices and Circuits Spring 2007 March 16, 2007 - Homework #4 Due - March 23, 2007

#### **Problem 1**

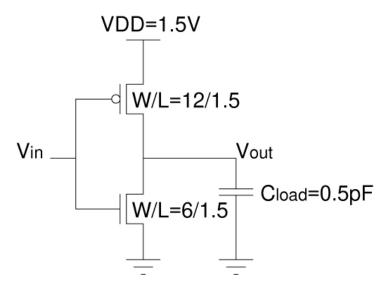

Consider the CMOS inverter pictured below. Take channel length modulation into account.

| Parameter | NMOS                    | PMOS                    |

|-----------|-------------------------|-------------------------|

| $V_{TO}$  | 0.5 V                   | -0.5 V                  |

| μ         | 220 cm <sup>2</sup> /Vs | 110 cm <sup>2</sup> /Vs |

| λ         | 0.1 V <sup>-1</sup>     | $0.1 \text{ V}^{-1}$    |

| Tox       | 15 nm                   | 15 nm                   |

## • Dimensions of W and L are in μm

- a) Calculate V<sub>M</sub>, the voltage midpoint.

- b) Calculate A<sub>V</sub>, the voltage gain at V<sub>in</sub>=V<sub>M</sub>.

- c) Calculate N<sub>ML</sub> and N<sub>MH</sub>, the noise margin low and noise margin high.

- d) Calculate t<sub>PHL</sub> and t<sub>PLH</sub>, the propagation delay from high-to-low and propagation delay from low-to-high.

- a) We set the drain current of the PMOS equal to the drain current of the NMOS, and plug in  $V_{in}=V_{out}=V_{M}$ .

$$V_{M} = 0.75 V$$

b) Voltage gain, Av= -(

$$g_{mn}+g_{mp}$$

)\*( $r_{on}||r_{op}$ )  $g_{mn}=g_{mp}=50\mu S$   $r_{on}=r_{op}=1.47M\Omega$  A<sub>v</sub>=-74

c)

$$NM_L = V_M + (V_{DD} - V_M)/A_V = 0.74V$$

$NM_H = V_{DD} - V_M + V_M/A_V = 0.74V$

d) propagation delay =

$$\Delta V*C/I$$

$\Delta V = 0.75V = 50\%$  of the total value

$C=500 fF$

$I_{D,pmos}=I_{D,nmos}=202 \mu A$

$$T_{PH} = T_{PL} = 1.856 \text{ ns}$$

#### **Problem 2**

We will now use the following SPICE model and compare our hand calculations from Problem 1 with simulated results.

.MODEL N15 NMOS LEVEL=1 VT0=0.5 TOX=1.5e-8 U0=220 LAMBDA=1.0e-1 +GAMMA=0.6 CJ=1e-4 CJSW=5e-10 PB=0.95 .MODEL P15 PMOS LEVEL=1 VT0=-0.5 TOX=1.5e-8 U0=110 LAMBDA=1.0e-1 +GAMMA=0.6 CJ=3e-4 CJSW=3.5e-10 PB=0.9

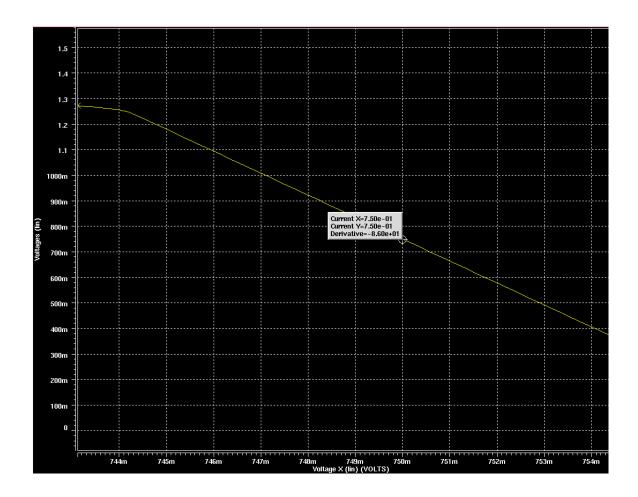

- a) Use the DC sweep on the input voltage to simulate transfer characteristics using SPICE. Compare  $V_M$ ,  $A_V$ ,  $N_{ML}$ ,  $N_{MH}$ , with the calculated results.

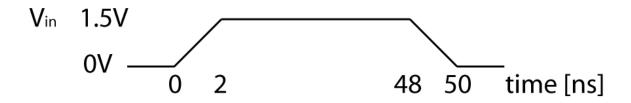

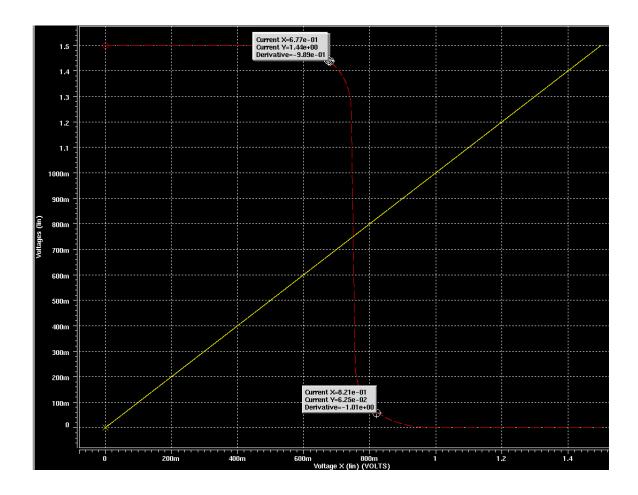

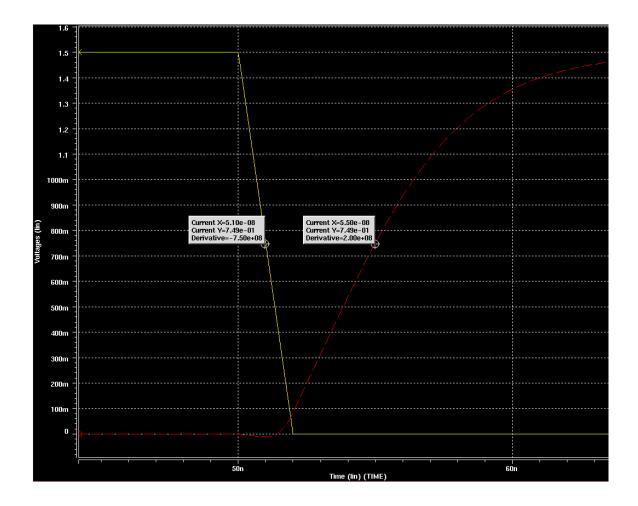

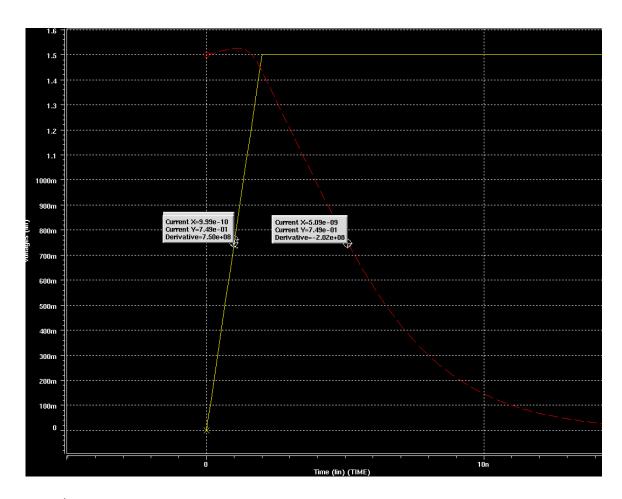

- b) Use the Pulse input to simulate an input waveform shown below using SPICE. Compare  $t_{PHL}$  and  $t_{PLH}$  with your hand calculations.

$$\label{eq:wester} \begin{split} We &~see~V_M \!\!=\!\! 0.75V. \\ N_{ML} &= V_{IL} \!\!-\!\! V_{OL} \sim 0.677V \!\!-\!\! 0.0625V \!\!=\!\! 0.615V \\ N_{MH} &= V_{OH} \!\!-\!\! V_{IH} \sim 1.44V \!\!-\!\! 0.821V \!\!=\!\! 0.619V \end{split}$$

$t_{PLH}\sim4ns$

$t_{PHL}\sim4.1ns$

# **Problem 3**

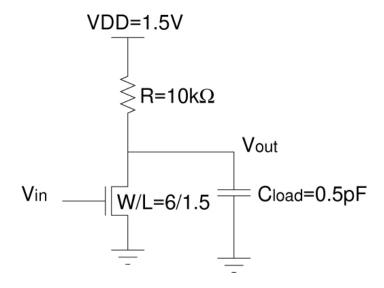

Consider the circuit below, which consists of an NMOS device and resistor load. Disregard channel length modulation for this problem.

- a) Calculate  $V_M$ ,  $V_{OH}$ ,  $V_{OL}$ . Remember, for hand calculations we assume  $V_{OH} = V_{MAX}$ , and  $V_{OL} = V_{MIN}$ .

- b) Calculate the voltage gain of this circuit, when  $V_{in}=V_{M}$ .

a) Set the current through the resistor equal to the current through the NMOS, with  $V_{in}=V_{out}=V_{M}$ .

$$\frac{V_{DD} - V_{M}}{R} = \frac{1}{2} \frac{W}{L} \mu C_{ox} (V_{M} - V_{Tn})^{2}$$

$$V_{M} = 1.16V$$

When the input is 0V (low), the NMOS is in cutoff, so no current flows. Therefore,  $V_{OH}=V_{MAX}=1.5V$

When the input is 1.5V (high), the NMOS is in triode. We must solve as we did earlier, setting the current through the resistor equal to the NMOS in triode.  $V_{in}$  is set to 1.5V.

$$\frac{V_{DD} - V_{\min}}{R} = \frac{W}{L} \mu C_{ox} \left( V_{DD} - \frac{V_{\min}}{2} - V_{Tn} \right) V_{\min}$$

$$V_{OL}=V_{MIN}=0.63V$$

b) The small signal gain of this circuit is  $-g_m*R$ .

$$g_m = \sqrt{2\frac{W}{L}\mu C_{ox}I_{DSat}} = 1.34\text{mA/V}$$

$$A_{V}=-1.34$$

## **Problem 4**

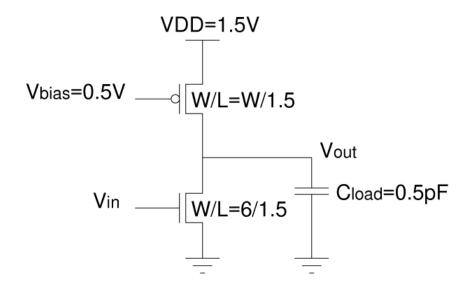

Consider the circuit below, which consists of an NMOS device and PMOS current source load. *Do not* neglect channel length modulation.

- a) Calculate the width of the PMOS device so its saturation current is 50μA.

- b) Calculate  $V_M$ ,  $V_{OH}$ ,  $V_{OL}$ . Remember, for hand calculations we assume  $V_{OH}=V_{MAX}$ , and  $V_{OL}=V_{MIN}$ .

- c) Calculate the voltage gain of this circuit, when V<sub>in</sub>=V<sub>M</sub>.

a)

$$50 \mu A = \frac{1}{2} \frac{W}{1.5} \mu_p C_{ox} (1 - 0.5)^2$$

Width of device, W = 23.7 microns

b) Setting the saturation drain current of the NMOS equal to that of the PMOS, we find

$$V_M = 1.175V$$

When the input is low, the NMOS is in cutoff, therefore  $V_{\text{OH}}\!\!=\!\!V_{\text{DD}}$

When the input is high, the NMOS is in triode. Setting the current through the NMOS equal to the PMOS,

$$\frac{1}{2} \frac{23.7}{1.5} \mu_p C_{ox} (1 - 0.5)^2 (1 + .1(V_{DD} - V_{min})) = \frac{6}{1.5} \mu C_{ox} \left( V_{DD} - \frac{V_{min}}{2} - 0.5 \right) V_{min}$$

$$V_{MIN} = V_{OL} = 0.33 V$$

c) For this circuit, the voltage gain is  $\,$  -g\_{mn} \* (r\_{on} || r\_{op})

$$g_m = \sqrt{2 \frac{W}{L} \mu C_{ox} I_{DSat}} = 0.144 \text{ mA/V}$$

$$r_{on} = r_{op} = \frac{1}{\lambda I_D} \rightarrow I_D = 50 \mu A , r_o = 200 k\Omega$$

$$A_{v} = -14$$