# **ENCS 333**

## (HOMEWORK #5)

Student name: Fadi Armoush

**Student number: <u>1160302</u>**

**Instructor: Dr. Khader Mohammad**

Section: 1

#### **Question one:**

11 VDD d Ground output B 1 A 6.round 2) output = (A + BC) Since the PMOS connected to the ground it is pop pseudo NMos circuits. [3] yes of course, Since it is used less un unnevers of transistors than fully complementary CMOS, OF In abbition it is more faster than it.

#### Question two:

First we need to implement a four input XOR gate, we know that XOR gate is odd function (i.e. the function is one when the number of ones from inputs is odd).

Truth table for 4-input XOR gate:

| A | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

**3** | P a g e

| 1 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

### So, function is:

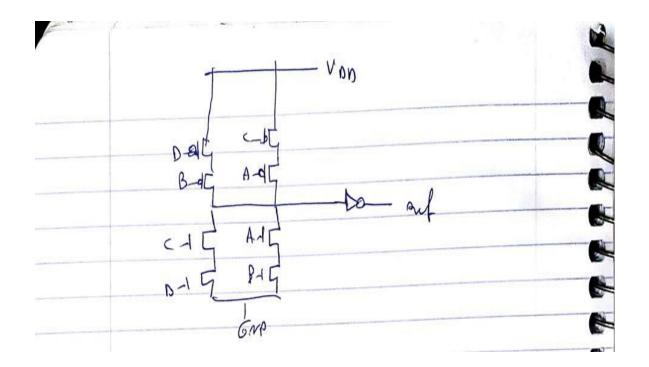

Then we will build the layout:

From the previous graph:

Delay=1.54ns-1.50ns=0.4ns < 0.5ns  $\rightarrow$  our design is accepted.

Also It obvious from the layout that our design occupies less than 500 square microns.

From our result, we see that our design work correctly as four input XOR gate.  $\rightarrow$  our work is accepted.

**Prepared by**

Fadi armoush

1160302