### What are embedded systems doing?

#### **Typical functionalities**

Measuring physical variables (sensing) Storing data Processing sensor signals and data Influencing physical variables (actuating) Monitoring Supervising Enable manual and automatic operation In one word: **Control**

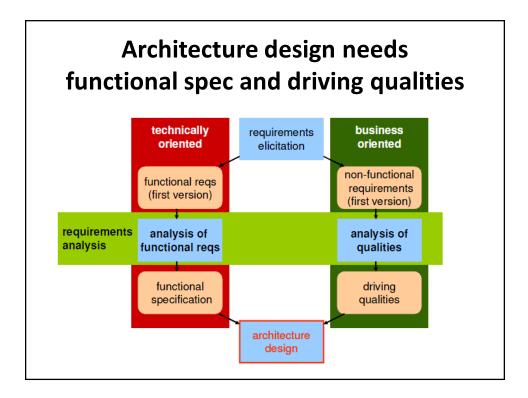

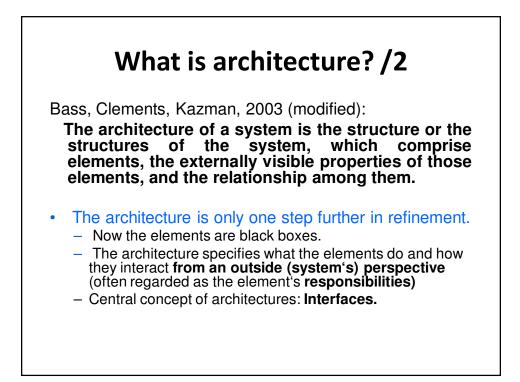

Bass, Clements, Kazman, 2003 (modified):

The architecture of a system is the structure or the structures of the system, which comprise elements, the externally visible properties of those elements, and the relationship among them.

- The architecture defines elements of the system.

Architecture design is the first phase in which the system is no longer a black box.

- The designer begins to structure the system into parts.

- Architecture manifests the earliest design decisions.

- Architecture is the blueprint for system integration.

7

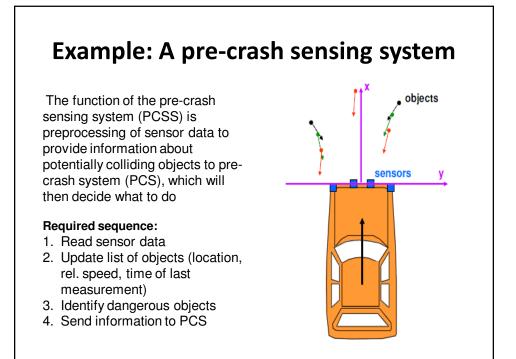

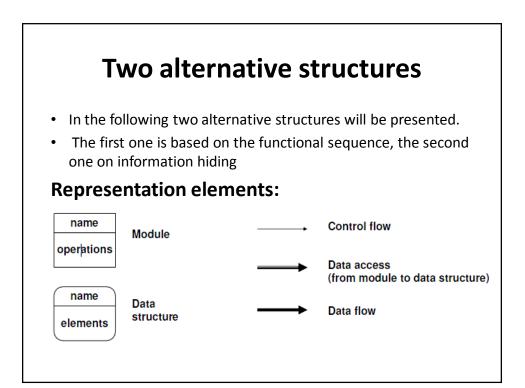

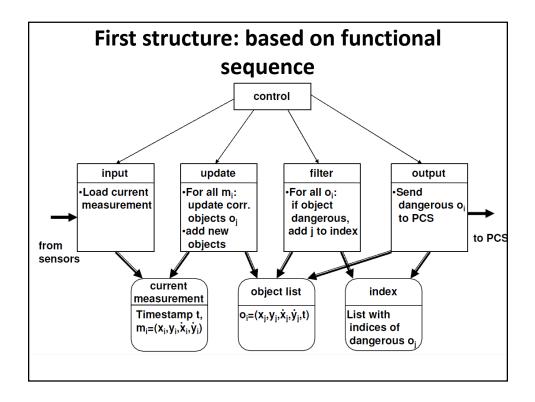

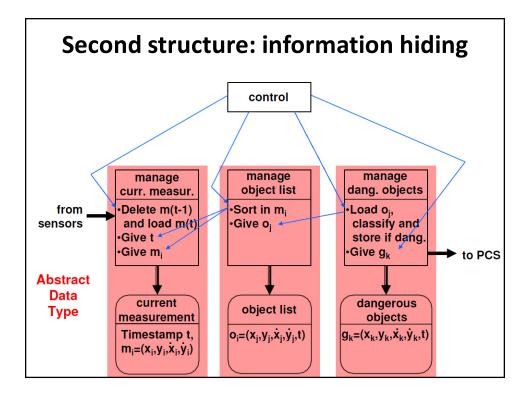

### Which is the better structure?

- Depends on criteria.

- Parnas, 1972:

- Best criterion for modularization is maintainability/modifiability, i.e. the support of changes.

- Changes mostly affect data structures

- Example:

- Objects shall be stored in polar coordinates instead of Cartesian coordinates.

- Changes in first structure: 3 Modules

- Changes in second structure: 1 Module

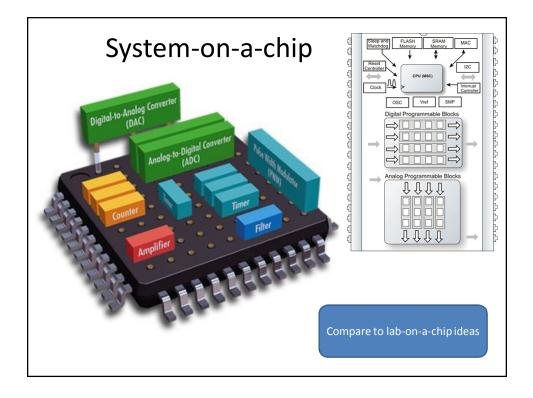

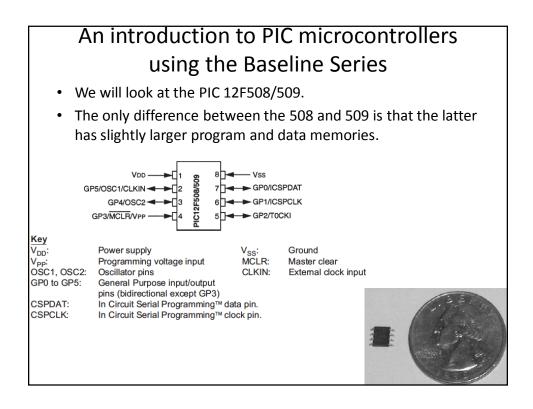

#### overview

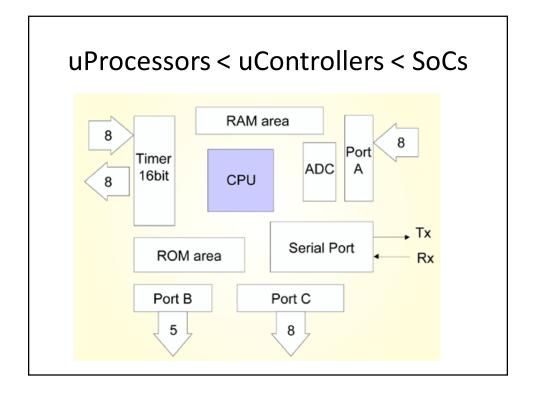

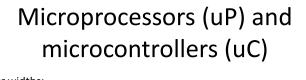

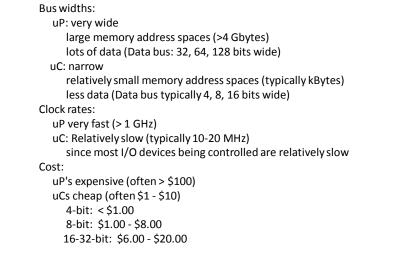

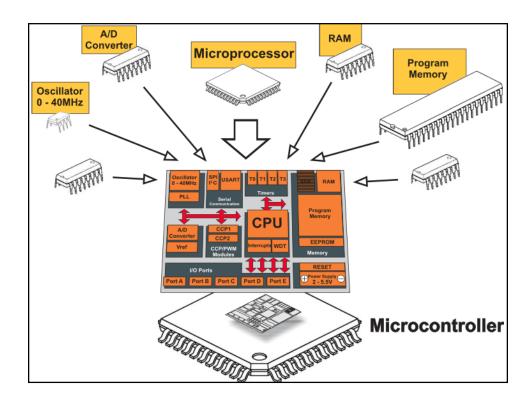

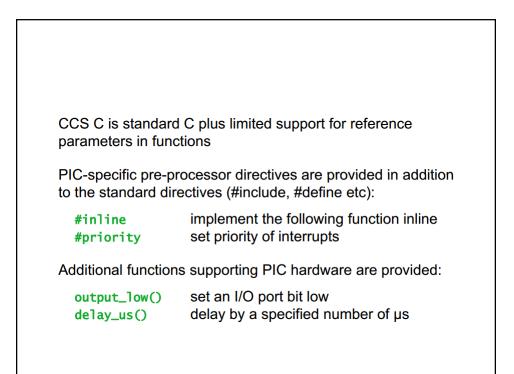

Microcontroller architecture. Address modes and instruction sets. Subroutines and interrupts. Handling software tools including IDE, editor, assembler, simulator and C compiler. Interface techniques including parallel, serial, timer, and analogue peripheral interface.

#### Memory – cont.

- Static RAM (SRAM)

- Each memory cell is designed as a simple flip-flop.

- Data is held only as long as power is supplied (volatile).

- Consume very little power, and can retain its data down to a low voltage (around 2 V).

- Each cell taking six transistors, SRAM is not a high-density technology.

- EPROM (Erasable Programmable Read-Only Memory)

- erased by exposing it to intense ultraviolet light.

- each memory cell is made of a single MOS transistor (very high density and robust)

- Within the transistor there is embedded a 'floating gate'. Using a technique known as hot electron injection (HEI), the floating gate can be charged. When it is not charged, the transistor behaves normally and the cell output takes one logic state when activated. When it is charged, the transistor no longer works properly and it no longer responds when it is activated. The charge placed on the floating gate is totally trapped by the surrounding insulator. Hence EPROM technology is non-volatile.

- Requires quartz window and ceramic packaging.

- As a technology, EPROM has now almost completely given way to Flash

| Memory – cont.                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>EEPROM (Electrically Erasable Programmable Read-<br/>Only Memory)</li> </ul>                                                                                                                          |  |  |  |  |  |

| <ul> <li>Uses floating gate technology.</li> <li>This is known as Nordheim–Fowler tunnelling (NFT).</li> <li>With NFT, it is possible to electrically erase the memory cell as well as write to it.</li> </ul> |  |  |  |  |  |

| <ul> <li>To allow this to happen, a number of switching transistors need to<br/>be included around the memory element itself, so the high density<br/>of EPROM is lost.</li> </ul>                             |  |  |  |  |  |

| <ul> <li>EEPROM is non-volatile         <ul> <li>Because the charge on the floating gate is totally trapped by the surrounding insulator</li> <li>Write and erase byte by byte.</li> </ul> </li> </ul>         |  |  |  |  |  |

| • Flash                                                                                                                                                                                                        |  |  |  |  |  |

| <ul> <li>A further evolution of floating-gate technology.</li> <li>can only erase in blocks.</li> <li>Non-volatile</li> </ul>                                                                                  |  |  |  |  |  |

|                                                                                                                                                                                                                |  |  |  |  |  |

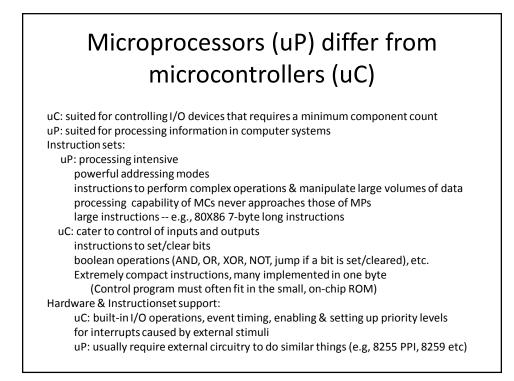

- Reduced Instruction Set Computer (RISC)

- Used in: SPARC, ALPHA, Atmel AVR, etc.

- Few instructions (usually < 50)</li>

- Only a few addressing modes

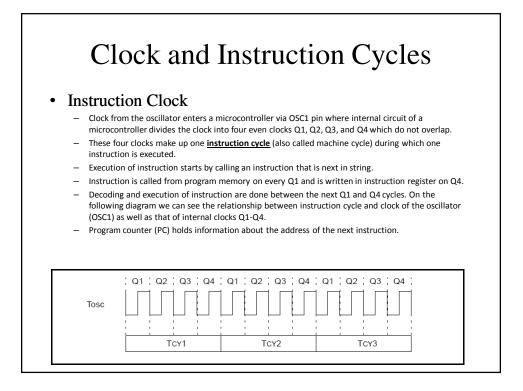

- Executes 1 instruction in 1 internal clock cycle (Tcyc)

- Complex Instruction Set Computer (CISC)

- Used in: 80X86, 8051, 68HC11, etc.

- Many instructions (usually > 100)

- Several addressing modes

- Usually takes more than 1 internal clock cycle (Tcyc) to execute

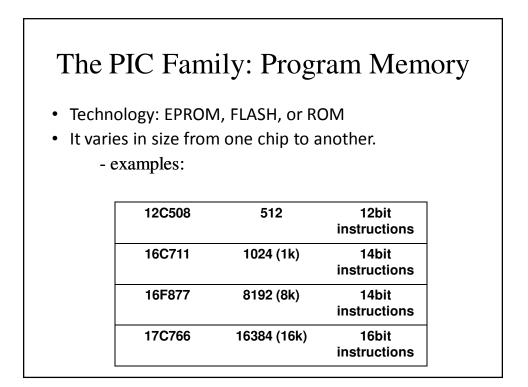

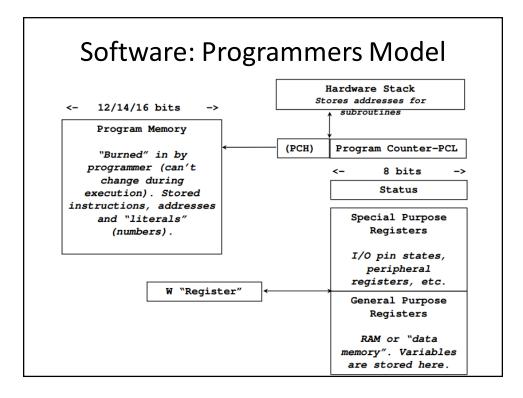

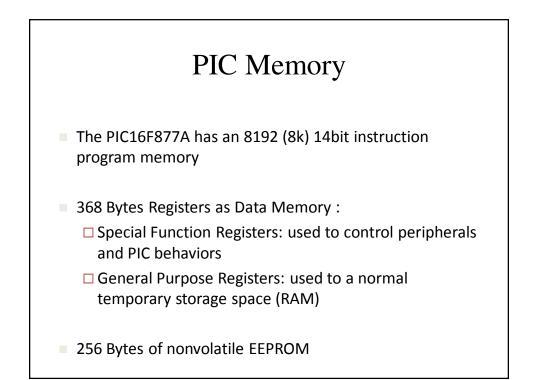

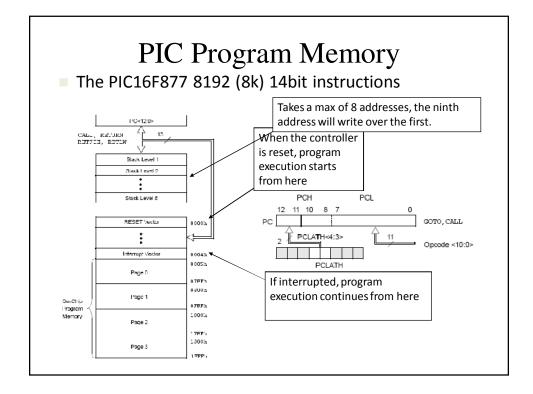

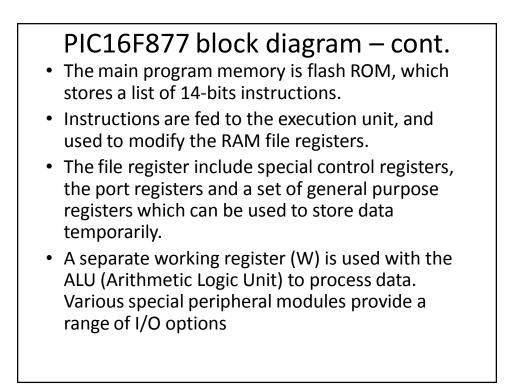

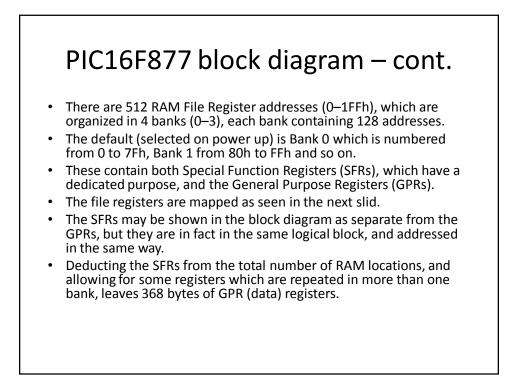

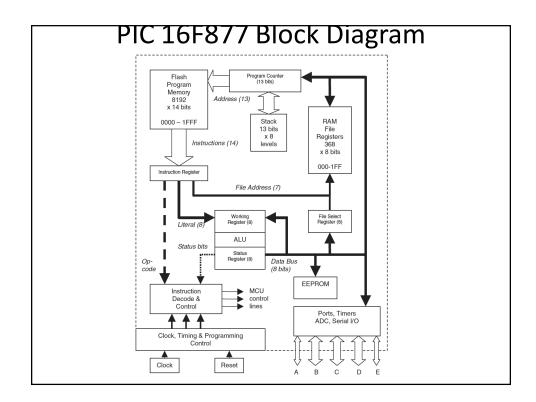

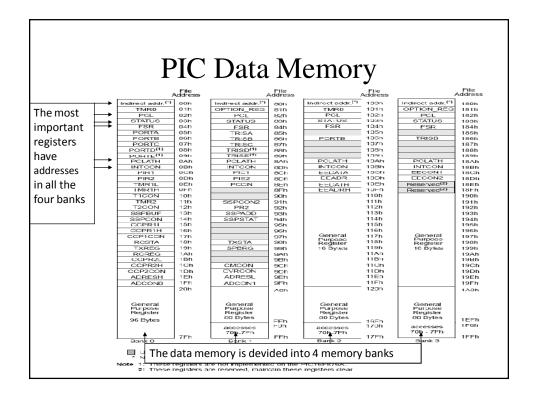

# The PIC Family: Data Memory

• PICs use general purpose "File registers" for RAM (each register is 8bits for all PICs)

- examples:

| 12C508 | 25B RAM                               |

|--------|---------------------------------------|

| 16C71C | 36B RAM                               |

| 16F877 | 368B RAM + 256B of nonvolatile EEPROM |

| 17C766 | 902B RAM                              |

|        |                                       |

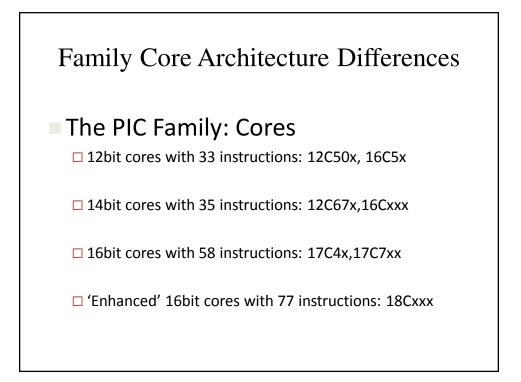

## Comparison of 8-bit PIC families

| Family              | Example devices                    | Instruction<br>word size | Stack size<br>(words) | Number of<br>instructions          | Interrupt vectors |

|---------------------|------------------------------------|--------------------------|-----------------------|------------------------------------|-------------------|

| Baseline            | 10F200, 12F508,<br>16F57           | 12 bit                   | 2                     | 33                                 | None              |

| Mid range           | 12F609, 16F84A,<br>16F631, 16F873A | 14 bit                   | 8                     | 35                                 | 1                 |

| High<br>Performance | 18F242, 18F2420                    | 16 bit                   | 32                    | 75, including<br>hardware multiply | 2 (prioritised)   |

- Every member of any one family shares the same core architecture and instruction set.

- The processing power is defined to some extent by the parameters quoted, for example the instruction word size, and the number of instructions.

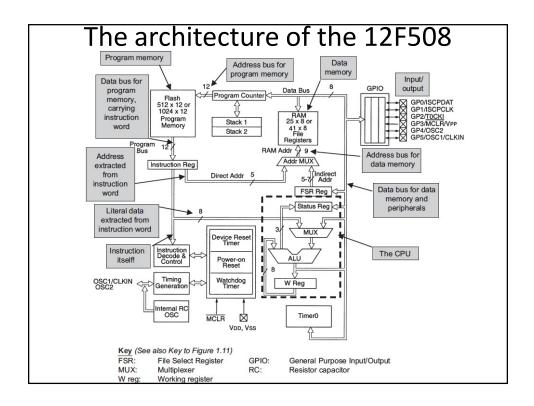

### The architecture of the 12F508 – cont.

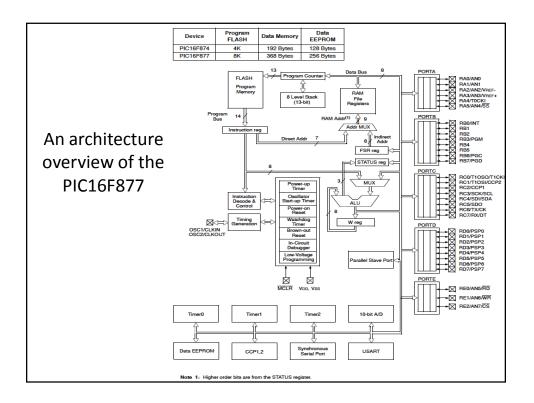

- As this microcontroller is a RISC computer, each instruction word must carry not only the instruction code itself, but also any address or data information needed.

- Depending on the instruction itself, five bits of the instruction word may carry address information and hence be sent down the 'Direct Addr' bus to the address multiplexer ('Addr MUX'). Eight bits of the instruction word may carry a data byte that is to be used as literal data for the execution of that instruction. This goes to the multiplexer ('MUX'), which feeds into the ALU. Finally, there is the instruction data itself, which feeds into the 'Instruction Decode and Control' unit.

- A 'Power-on Reset' function detects when power is applied and holds the microcontroller in a Reset condition while the power supply stabilizes.

- The MCLR input can be used to place the CPU in a Reset condition and to force the program to start again.

- An internal clock oscillator ('Internal RC OSC') is provided so that no external pins whatsoever need be committed to this function.

- External oscillator connections can, however, be made, using input/output pins GP4 and GP5. The oscillator signal is conditioned for use through the microcontroller in the 'Timing Generation' unit.

- The 'Watchdog Timer' is a safety feature, used to force a reset in the processor if it crashes.

## **PIC Programming Procedure**

- For example: in programming an embedded PIC featuring electronically erasable programmable read-only memory (EEPROM). The essential steps are:

- Step 1: On a PC, type the program, successfully compile it and then generate the HEX file.

- Step 2: Using a PIC device programmer, upload the HEX file into the PIC. This step is often called "burning".

- Step 3: Insert your PIC into your circuit, power up and verify the program works as expected. This step is often called "dropping" the chip. If it isn't, you must go to Step 1 and debug your program and repeat burning and dropping.

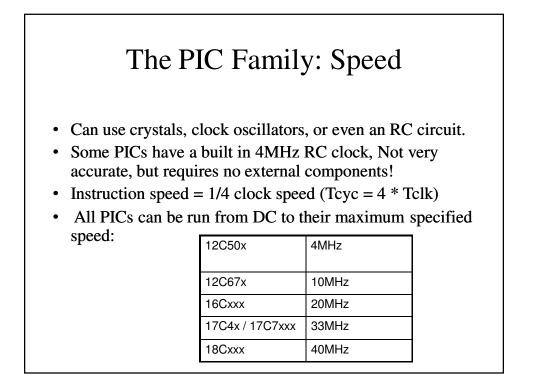

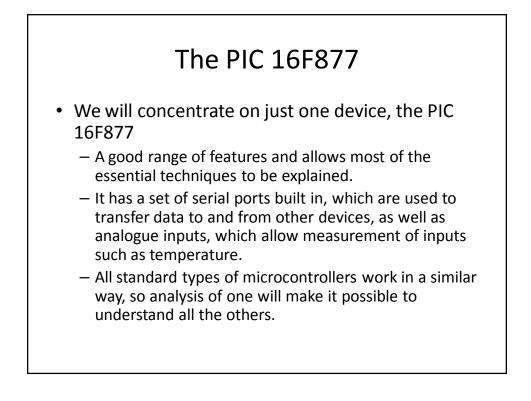

#### **High Performance RISC CPU:**

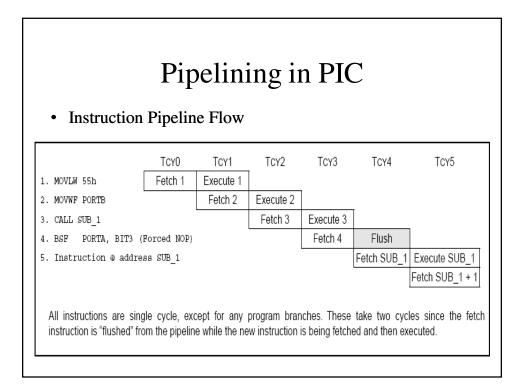

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches, which are two-cycle

- Operating speed: DC 20 MHz clock input DC 200 ns instruction cycle

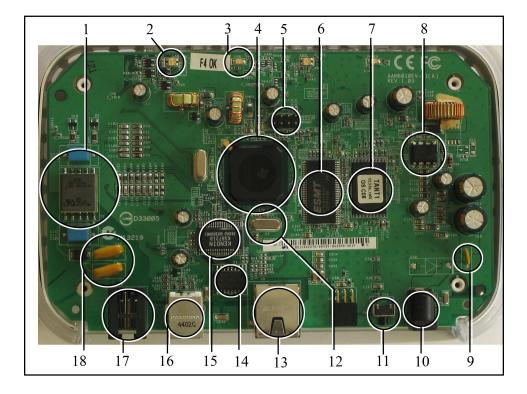

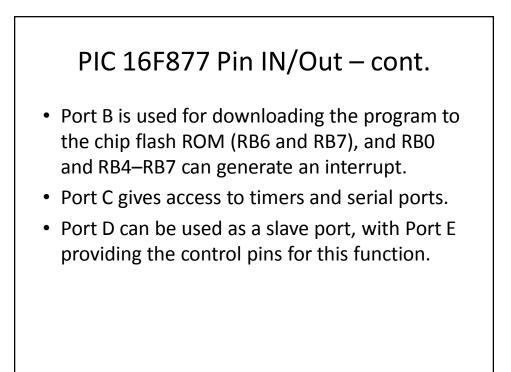

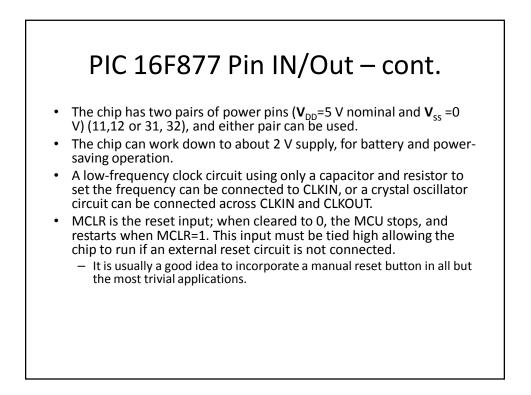

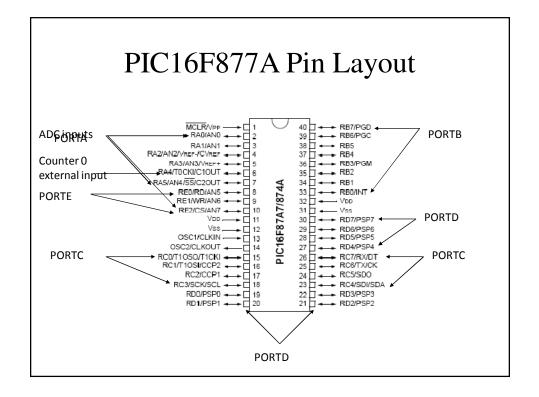

## PIC 16F877 Pin IN/Out

- The chip can be obtained in different packages, such as conventional 40-pin DIP (Dual In-Line Package), square surface mount or socket format.

- Most of the pins are for input and output, and arranged as 5 ports: port A (5 pins), port B(8), C(8), D(8) and E(3), giving a total of 32 I/O pins.

- These can all operate as simple digital I/O pins, but most have more than one function.

- The mode of operation of each is selected by initializing various control registers within the chip.

- Note, in particular, that Ports A and E become ANALOGUE INPUTS by default (on power up or reset), so they have to set up for digital I/O if required.

| PIC 16F877 Pin IN/Out – cont.      |                 |    |    |                 |                                         |  |

|------------------------------------|-----------------|----|----|-----------------|-----------------------------------------|--|

|                                    |                 |    |    |                 |                                         |  |

|                                    |                 |    |    |                 |                                         |  |

| Reset = 0, Run = 1                 | MCLR            | 1  | 40 | RB7             | Port B, Bit 7 (Prog. Data, Interrupt)   |  |

| Port A, Bit 0 (Analogue AN0)       | RA0             | 2  | 39 | RB6             | Port B, Bit 6 (Prog. Clock, Interrupt)) |  |

| Port A, Bit 1 (Analogue AN1)       | RA1             | 3  | 38 | RB5             | Port B, Bit 5 (Interrupt)               |  |

| Port A, Bit 2 (Analogue AN2)       | RA2             | 4  | 37 | RB4             | Port B, Bit 4 (Interrupt)               |  |

| Port A, Bit 3 (Analogue AN3)       | RA3             | 5  | 36 | RB3             | Port B, Bit 3 (LV Program)              |  |

| Port A, Bit 4 (Timer 0)            | RA4             | 6  | 35 | RB2             | Port B, Bit 2                           |  |

| Port A, Bit 5 (Analogue AN4)       | RA5             | 7  | 34 | RB1             | Port B, Bit 1                           |  |

| Port E, Bit 0 (AN5, Slave control) | RE0             | 8  | 33 | RB0             | Port B, Bit 0 (Interrupt)               |  |

| Port E, Bit 1 (AN6, Slave control) | RE1             | 9  | 32 | V <sub>DD</sub> | +5V Power Supply                        |  |

| Port E, Bit 2 (AN7, Slave control) | RE2             | 10 | 31 | Vss             | 0V Power Supply                         |  |

| +5V Power Supply                   | V <sub>DD</sub> | 11 | 30 | RD7             | Port D, Bit 7 (Slave Port)              |  |

| 0V Power Supply                    | Vss             | 12 | 29 | RD6             | Port D, Bit 6 (Slave Port)              |  |

| (CR clock) XTAL circuit            | CLKIN           | 13 | 28 | RD5             | Port D, Bit 5 (Slave Port)              |  |

| XTAL circuit                       | CLKOUT          | 14 | 27 | RD4             | Port D, Bit 4 (Slave Port)              |  |

| Port C, Bit 0 (Timer 1)            | RC0             | 15 | 26 | RC7             | Port C, Bit 7 (Serial Ports)            |  |

| Port C, Bit 1 (Timer 1)            | RC1             | 16 | 25 | RC6             | Port C, Bit 6 (Serial Ports)            |  |

| Port C, Bit 2 (Timer 1)            | RC2             | 17 | 24 | RC5             | Port C, Bit 5 (Serial Ports)            |  |

| Port C, Bit 3 (Serial Clocks)      | RC3             | 18 | 23 | RC4             | Port C, Bit 4 (Serial Ports)            |  |

| Port D, Bit 0 (Slave Port)         | RD0             | 19 | 22 | RD3             | Port D, Bit 3 (Slave Port)              |  |

| Port D, Bit 1 (Slave Port)         | RD1             | 20 | 21 | RD2             | Port D, Bit 2 (Slave Port)              |  |

|                                    |                 |    |    |                 |                                         |  |

|                                    |                 |    |    |                 |                                         |  |

|                                    |                 |    |    |                 |                                         |  |

|                                    |                 |    |    |                 |                                         |  |

|                                    |                 |    |    |                 |                                         |  |

| ,                                                                                                                                                                              | File<br>Address | ,                    | File<br>Address |                     | File<br>Address |                         | File<br>Addres |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr.(*)                                                                                                                                                              | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)   | 100h            | Indirect addr.          | 180h           |

| TMBO                                                                                                                                                                           | 01h             | OPTION REG           | 81h             | TMB0                | 101h            | OPTION REG              | 181h           |

| PCL                                                                                                                                                                            | 02h             | PCL                  | 82h             | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                                                                                                                                                                         | 03h             | STATUS               | 83h             | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                                                                                                                                                                            | 04h             | FSR                  | 84h             | FSR                 | 104h            | FSR                     | 184h           |

| POBTA                                                                                                                                                                          | 05h             | TRISA                | 85h             |                     | 105h            | 1311                    | 185h           |

| PORTB                                                                                                                                                                          | 06h             | TRISA                | 86h             | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                                                                                                                                                                          | 07h             | TRISC                | 87h             | 1 OITE              | 107h            |                         | 187h           |

| POBTD <sup>(1)</sup>                                                                                                                                                           | 08h             | TBISD <sup>(1)</sup> | 88h             |                     | 108h            |                         | 188h           |

| POBTE(1)                                                                                                                                                                       | 09h             | TRISE®               | 89h             |                     | 109h            |                         | 189h           |

| PCLATH                                                                                                                                                                         | 0Ah             | PCLATH               | 8Ah             | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                                                                                                                                                                         | OBh             | INTCON               | 8Bh             | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIB1                                                                                                                                                                           | OCh             | PIE1                 | 8Ch             | EEDATA              | 10Ch            | EECON1                  | 18Ch           |

| PIR2                                                                                                                                                                           | ODh             | PIE2                 | 8Dh             | EEADR               | 10Dh            | EECON2                  | 180h           |

| TMB1L                                                                                                                                                                          | OEh             | PCON                 | 8Eh             | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMB1H                                                                                                                                                                          | OFh             | FCON                 | 8Fh             | EEADBH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TICON                                                                                                                                                                          | 10h             |                      | 90h             | EEADAH              | 110h            | Reserved                | 190h           |

| TMB2                                                                                                                                                                           | 11h             | SSPCON2              | 91h             |                     | 111h            |                         | 191h           |

| T2CON                                                                                                                                                                          | 12h             | PR2                  | 92h             |                     | 112h            |                         | 192h           |

| SSPBUE                                                                                                                                                                         | 13h             | SSPADD               | 92h<br>93h      |                     | 113h            |                         | 192h           |

| SSPEOR                                                                                                                                                                         | 14h             | SSPADD               | 93h<br>94h      |                     | 114h            |                         | 193h           |

| CCPB1L                                                                                                                                                                         | 140<br>15h      | SSPSTAL              | 94n<br>95h      |                     | 115h            |                         | 194h           |

| CCPRIL                                                                                                                                                                         | 16h             |                      | 95h<br>96h      |                     | 116h            |                         | 195h           |

| CCP1CON                                                                                                                                                                        | 17h             |                      | 96n<br>97h      | General             | 117h            | General                 | 196h           |

| BCSTA                                                                                                                                                                          | 18h             | TXSTA                | 97h<br>98h      | Purpose             | 118h            | Purpose                 | 198h           |

| TXREG                                                                                                                                                                          | 19h             | SPBRG                |                 | Register            | 119h            | Register                | 199h           |

| RCREG                                                                                                                                                                          | 1Ah             | SPBRG                | 99h             | 16 Bytes            | 11Ah            | 16 Bytes                | 199h           |

|                                                                                                                                                                                | 1Bh             |                      | 9Ah             |                     | 11Bh            |                         | 19Bh           |

| CCPR2L                                                                                                                                                                         | 1Ch             |                      | 9Bh             |                     | 11Ch            |                         |                |

| CCPR2H                                                                                                                                                                         | 1Dh             |                      | 9Ch             |                     | 11Dh            |                         | 19Ch           |

| CCP2CON                                                                                                                                                                        | 1Eh             | ADRESL               | 9Dh             |                     | 11Eh            |                         | 19Dh<br>19Eh   |

| ADRESH                                                                                                                                                                         | 1Eh             |                      | 9Eh             |                     | 11Eh            |                         |                |

| ADCON0                                                                                                                                                                         |                 | ADCON1               | 9Fh             |                     |                 |                         | 19Fh           |

|                                                                                                                                                                                | 20h             |                      | A0h             |                     | 120h            |                         | 1A0h           |

| General                                                                                                                                                                        |                 | General              |                 | General             |                 | General                 |                |

| Purpose<br>Register                                                                                                                                                            |                 | Purpose<br>Register  |                 | Purpose<br>Register |                 | Purpose<br>Register     |                |

| e e e e e e e e e e e e e e e e e e e                                                                                                                                          |                 | 80 Bytes             |                 | 80 Bytes            |                 | 80 Bytes                | 100            |

| 96 Bytes                                                                                                                                                                       |                 |                      | EFh             |                     | 16Fh            |                         | 1EFr           |

|                                                                                                                                                                                | 7Eb             | accesses<br>70h-7Fh  | FOh             | accesses<br>70h-7Fh | 170h<br>17Fh    | accesses<br>70h - 7Fh   | 1FOh           |

| Bank 0                                                                                                                                                                         |                 | Bank 1               |                 | Bank 2              |                 | Bank 3                  |                |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>Not a physical register.</li> <li>Note 1: These registers are not implemented on the PIC16F876.</li> </ul> |                 |                      |                 |                     |                 |                         |                |

|                                                                                                                                                                                |                 | re reserved, main    |                 |                     |                 |                         |                |

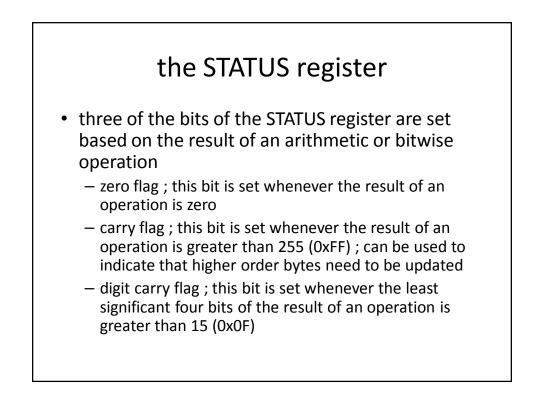

|         | Special Function Register<br>"STATUS Register"                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|         |                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|         | R/W-0         R/W-0         R-1         R-1         R/W-x         R/W-x         R/W-x           IRP         RP1         RP0         TO         PD         Z         DC         C           bit 7         bit 0                                          |  |  |  |  |  |  |  |

| bit 7   | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>o = Bank 0, 1 (00h - FFh)                                                                                                                                |  |  |  |  |  |  |  |

| bit 6-5 |                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| bit 4   | TO: Time-out bit<br>1 = After power-up, CLRWDT Instruction, or SLEEP Instruction<br>0 = A WDT time-out occurred                                                                                                                                         |  |  |  |  |  |  |  |

| bit 3   | PD: Power-down bit     1 = After power-up or by the CLRWDT instruction     o = By execution of the SLEEP instruction                                                                                                                                    |  |  |  |  |  |  |  |

| bit 2   | <ul> <li>Z. Zero bit</li> <li>1 - The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                             |  |  |  |  |  |  |  |

| bit 1   |                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| bit 0   | C: Cany/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                           |  |  |  |  |  |  |  |

|         | Note: For borrow, the polarity is reversed. A subtraction is executed by adding the two's<br>complement of the second operand. For rotate (RRF, RLF) instructions, this bit is<br>loaded with either the high, or low order bit of the source register. |  |  |  |  |  |  |  |

|         | Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         - n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown                                                    |  |  |  |  |  |  |  |

| "INTCON Register" |                             |                                                                                       |              |            |              |                             |       |       |

|-------------------|-----------------------------|---------------------------------------------------------------------------------------|--------------|------------|--------------|-----------------------------|-------|-------|

|                   | R/W-0                       | R/W-0                                                                                 | R/W-0        | R/W-0      | R/W-0        | R/W-0                       | R/W-0 | R/W-x |

|                   | GIE                         | PEIE                                                                                  | TMROIE       | INTE       | RBIE         | TMR0IF                      | INTE  | RBIF  |

|                   | bit 7                       |                                                                                       |              |            |              |                             |       | bit C |

| bit 7             | GIE: Global                 | Interrupt E                                                                           | nable bit    |            |              |                             |       |       |

|                   | 1 = Enables<br>0 = Disables |                                                                                       |              | s          |              |                             |       |       |

| bit 6             | PEIE: Peripi                |                                                                                       |              | bit        |              |                             |       |       |

|                   | 1 = Enables<br>0 = Disables |                                                                                       |              |            |              |                             |       |       |

| bit 5             | TMROIE: TM                  | 1R0 Overflo                                                                           | ow Interrupt | Enable bit |              |                             |       |       |

|                   | 1 = Enables<br>0 = Disables |                                                                                       |              |            |              |                             |       |       |

| bit 4             | INTE: RB0/I                 |                                                                                       |              | nable bit  |              |                             |       |       |

|                   | 1 = Enables<br>0 = Disables |                                                                                       |              |            |              |                             |       |       |

| bit 3             | RBIE: RB P                  |                                                                                       |              |            |              |                             |       |       |

|                   |                             | 1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt |              |            |              |                             |       |       |

| bit 2             | TMR0IF: TM                  | IR0 Overfic                                                                           | ow Interrupt | Flag bit   |              |                             |       |       |

|                   | 1 = TMR0 re<br>o = TMR0 re  |                                                                                       |              |            | ared in soft | ware)                       |       |       |

| bit 1             | INTF: RB0/I                 |                                                                                       |              |            |              |                             |       |       |

|                   | 1 = The RB0<br>0 = The RB0  |                                                                                       |              |            |              | red in softwa               | are)  |       |

| bit 0             | RBIF: RB P                  | ort Change                                                                            | Interrupt Fi | ag bit     |              |                             |       |       |

|                   |                             | Reading PC                                                                            |              |            |              | match condit<br>n and allow |       |       |

### X14 Instruction set

- 35 instructions

- -Byte Oriented Operations

- -Bit Oriented Operations

- -Literal and control Operations

| Mnemonic, |                                | Description                                            | Cycles      |          | 14-Bit (  | Opcode   | •          | Status        | Notes    |

|-----------|--------------------------------|--------------------------------------------------------|-------------|----------|-----------|----------|------------|---------------|----------|

| Ope       | rands                          | Description                                            |             | MSb      |           |          | LSb        | Affected      | Notes    |

|           |                                | BYTE-ORIENTED FILE REGIS                               | TER OPE     | RATIO    | NS        |          |            |               |          |

| ADDWF     | f, d                           | Add W and f                                            | 1           | 00       | 0111      | dfff     | ffff       | C,DC,Z        | 1,2      |

| ANDWF     | f, d                           | AND W with f                                           | 1           | 00       | 0101      | dfff     | ffff       | z             | 1,2      |

| CLRF      | f                              | Clear f                                                | 1           | 00       | 0001      | lfff     | ffff       | z             | 2        |

| CLRW      | -                              | Clear W                                                | 1           | 00       | 0001      | 0xxx     | XXXXX      | Z             |          |

| COMF      | f, d                           | Complement f                                           | 1           | 00       | 1001      | dfff     | ffff       | Z             | 1,2      |

| DECF      | f, d                           | Decrement f                                            | 1           | 00       | 0011      | dfff     | ffff       | Z             | 1,2      |

| DECFSZ    | f, d                           | Decrement f, Skip if 0                                 | 1(2)        | 00       | 1011      | dfff     | ffff       |               | 1,2,3    |

| INCE      | f, d                           | Increment f                                            | 1           | 00       | 1010      | dfff     | ffff       | Z             | 1,2      |

| INCFSZ    | SZ f. d Increment f. Skip if 0 |                                                        | 1(2)        | 00       | 1111      | dfff     | ffff       |               | 1.2.3    |

| IORWF     | f, d                           | Inclusive OR W with f                                  | 1 i         | 00       | 0100      | dfff     | ffff       | z             | 1.2      |

| MOVE      | f, d                           | Move f                                                 | 1           | 0.0      | 1000      | dfff     | ffff       | 7             | 1,2      |

| MOVWE     | f                              | Move W to f                                            | i i         | 00       |           | lfff     |            | _             | -,-      |

| NOP       | -                              | No Operation                                           | 1           | 0.0      | 0000      | 0xx0     | 0000       |               |          |

| BLE       | f, d                           | Rotate Left f through Carry                            | l i         | 00       |           | dfff     |            | С             | 1.2      |

| RRF       | f, d                           | Rotate Right f through Carry                           | l i         | 00       |           | dfff     |            | č             | 1.2      |

| SUBWE     | f, d                           | Subtract W from f                                      | l i         | 00       |           | dfff     |            | C.DC.Z        | 1,2      |

| SWAPF     | f, d                           | Swap nibbles in f                                      | l i         | 00       |           | dfff     |            | 0,00,2        | 1.2      |

| XORWE     | f, d                           | Exclusive OB W with f                                  | i           | 00       | 0110      | dfff     |            | 7             | 1.2      |

| XORWE     | 1, 0                           |                                                        |             |          |           | dill     | 1111       | 2             | 1,2      |

|           |                                | BIT-ORIENTED FILE REGIST                               |             |          |           |          |            |               |          |

| BCF       | f, b                           | Bit Clear f                                            | 1           | 01       |           | bfff     |            |               | 1,2      |

| BSF       | f, b                           | Bit Set f                                              | 1           | 01       |           | bfff     |            |               | 1,2      |

| BTFSC     | f, b                           | Bit Test f, Skip if Clear                              | 1 (2)       | 01       |           | bfff     |            |               | 3        |

| BTFSS     | f, b                           | Bit Test f, Skip if Set                                | 1 (2)       | 01       | 11bb      | bfff     | ffff       |               | 3        |

|           |                                | LITERAL AND CONTROL                                    |             |          |           |          |            |               |          |

| ADDLW     | k                              | Add literal and W                                      | 1           | 11       |           | kkkk     |            | C,DC,Z        |          |

| ANDLW     | k                              | AND literal with W                                     | 1           | 11       |           | kkkk     |            | z             |          |

| CALL      | k                              | Call subroutine                                        | 2           | 10       |           | kkkk     |            |               |          |

| CLRWDT    | -                              | Clear Watchdog Timer                                   | 1           | 00       | 0000      | 0110     | 0100       | TO,PD         |          |

| GOTO      | k                              | Go to address                                          | 2           | 10       |           | kkkk     |            |               |          |

| IORLW     | k                              | Inclusive OR literal with W                            | 1           | 11       |           | kkkk     |            | Z             |          |

| MOVLW     | k                              | Move literal to W                                      | 1           | 11       |           | kkkk     |            |               |          |

| RETFIE    | -                              | Return from interrupt                                  | 2           | 00       | 0000      | 0000     | 1001       |               |          |

| RETLW     | k                              | Return with literal in W                               | 2           | 11       | 01xx      | kkkk     | kkkk       |               |          |

| RETURN    | -                              | Return from Subroutine                                 | 2           | 00       | 0000      | 0000     | 1000       |               |          |

| SLEEP     | -                              | Go into standby mode                                   | 1           | 00       | 0000      | 0110     | 0011       | TO,PD         |          |

| SUBLW     | k                              | Subtract W from literal                                | 1           | 11       | 110x      | kkkk     | kkkk       | C,DC,Z        |          |

| XORLW     | k                              | Exclusive OR literal with W                            | 1           | 11       | 1010      | kkkk     | kkkk       | z             |          |

| Note 1:   | When an I/                     | O register is modified as a function of itself ( e.g., | MOVF POP    | RTB, :   | 1), the v | alue use | ed will b  | e that value  | present  |

|           | on the pins                    | themselves. For example, if the data latch is '1' for  | or a pin co | onfigure | ed as inc | out and  | is driver  | low by an     | external |

|           |                                | data will be written back with a '0'.                  |             |          |           |          |            |               |          |

| 2:        | If this instru                 | uction is executed on the TMR0 register (and, whe      | ere applica | able, d  | = 1), the | e presca | der will l | be cleared if | F .      |

|           |                                | o the Timer0 module.                                   |             |          |           |          |            |               |          |

| 3:        | If Program                     | Counter (PC) is modified, or a conditional test is t   | rue, the in | structio | on requir | res two  | cvcles     | The second    | cvcle is |

|           |                                |                                                        |             |          |           |          |            |               |          |

- Data Movement

- movf,movlw,movwf

- Arithmetic

- addlw,addwf,sublw,subwf,incf,decf

- Logical

- andlw,andwf,iorlw,iorwf,xorlw,xorwf,rrf,rlf,clrf,clrw,swapf,c omf

- Bit Operators

- bsf,bcf

- Branching

- goto,btfss,btfsc,decfsz,incfsz

- Subroutine

- call,return,retlw,retfie

- Misc.

- sleep,clrwdt,nop

| Mnemonic,<br>Operands |      | Description                  | Cycles       | 14-Bit Opcode |      |                     | •    | Status   | Notes |

|-----------------------|------|------------------------------|--------------|---------------|------|---------------------|------|----------|-------|

|                       |      | Description                  | Cycles       | MSb           |      |                     | LSb  | Affected | Notes |

|                       |      | BYTE-ORIENTED FILE           | REGISTER OPE | RATIC         | NS   |                     |      |          |       |

| ADDWF                 | f, d | Add W and f                  | 1            | 00            | 0111 | dfff                | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f, d | AND W with f                 | 1            | 00            | 0101 | dfff                | ffff | Z        | 1,2   |

| CLRF                  | f    | Clear f                      | 1            | 00            | 0001 | lfff                | ffff | Z        | 2     |

| CLRW                  | -    | Clear W                      | 1            | 00            | 0001 | 0xxx                | xxxx | Z<br>Z   |       |

| COMF                  | f, d | Complement f                 | 1            | 00            | 1001 | dfff                | ffff | Z        | 1,2   |

| DECF                  | f, d | Decrement f                  | 1            | 00            | 0011 | dfff                | ffff | Z        | 1,2   |

| DECFSZ                | f, d | Decrement f, Skip if 0       | 1(2)         | 00            | 1011 | dfff                | ffff |          | 1,2,3 |

| INCF                  | f, d | Increment f                  | 1            | 00            | 1010 | dfff                | ffff | Z        | 1,2   |

| INCFSZ                | f, d | Increment f, Skip if 0       | 1(2)         | 00            | 1111 | dfff                | ffff |          | 1,2,3 |

| IORWF                 | f, d | Inclusive OR W with f        | 1            | 00            | 0100 | dfff                | ffff | Z        | 1,2   |

| MOVF                  | f, d | Move f                       | 1            | 00            | 1000 | dfff                | ffff | Z        | 1,2   |

| MOVWF                 | f    | Move W to f                  | 1            | 00            | 0000 | lfff                | ffff |          |       |

| NOP                   | -    | No Operation                 | 1            | 00            | 0000 | $0 \times \times 0$ | 0000 |          |       |

| RLF                   | f, d | Rotate Left f through Carry  | 1            | 00            | 1101 | dfff                | ffff | С        | 1,2   |

| RRF                   | f, d | Rotate Right f through Carry | 1            | 00            | 1100 | dfff                | ffff | С        | 1,2   |

| SUBWF                 | f, d | Subtract W from f            | 1            | 00            | 0010 | dfff                | ffff | C,DC,Z   | 1,2   |

| SWAPF                 | f, d | Swap nibbles in f            | 1            | 00            | 1110 | dfff                | ffff | 87 88    | 1,2   |

| XORWF                 | f, d | Exclusive OR W with f        | 1            | 00            | 0110 | dfff                | ffff | Z        | 1,2   |

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction

| Onoran   | nic, | Description                 | Cycles        |      | 14-Bit | Opcod | e    | Status   |       |

|----------|------|-----------------------------|---------------|------|--------|-------|------|----------|-------|

| Operands |      | Description                 |               | MSb  |        |       | LSb  | Affected | Notes |

|          |      | BIT-ORIENTED FILE           | REGISTER OPER | ATIO | IS     |       |      |          |       |

| BCF      | f, b | Bit Clear f                 | 1             | 01   | 00bb   | bfff  | ffff |          | 1,2   |

| BSF      | f, b | Bit Set f                   | 1             | 01   | 01bb   | bfff  | ffff |          | 1,2   |

| BTFSC    | f, b | Bit Test f, Skip if Clear   | 1 (2)         | 01   | 10bb   | bfff  | ffff |          | 3     |

| BTFSS    | f, b | Bit Test f, Skip if Set     | 1 (2)         | 01   | 11bb   | bfff  | ffff |          | 3     |

|          |      | LITERAL AND CO              | NTROL OPERATI | ONS  |        |       |      |          |       |

| ADDLW    | k    | Add literal and W           | 1             | 11   | 111x   | kkkk  | kkkk | C,DC,Z   |       |

| ANDLW    | k    | AND literal with W          | 1             | 11   | 1001   | kkkk  | kkkk | Z        |       |

| CALL     | k    | Call subroutine             | 2             | 10   | 0kkk   | kkkk  | kkkk |          |       |

| CLRWDT   | -    | Clear Watchdog Timer        | 1             | 00   | 0000   | 0110  | 0100 | TO,PD    |       |

| GOTO     | k    | Go to address               | 2             | 10   | 1kkk   | kkkk  | kkkk |          |       |

| ORLW     | k    | Inclusive OR literal with W | 1             | 11   | 1000   | kkkk  | kkkk | z        |       |

| MOVLW    | k    | Move literal to W           | 1             | 11   | 00xx   | kkkk  | kkkk |          |       |

| RETFIE   | -    | Return from interrupt       | 2             | 00   | 0000   | 0000  | 1001 |          |       |

| RETLW    | k    | Return with literal in W    | 2             | 11   | 01xx   | kkkk  | kkkk |          |       |

| RETURN   | -    | Return from Subroutine      | 2             | 00   | 0000   | 0000  | 1000 |          |       |

| SLEEP    | -    | Go into standby mode        | 1             | 00   | 0000   | 0110  | 0011 | TO,PD    |       |

| SUBLW    | k    | Subtract W from literal     | 1             | 11   | 110x   | kkkk  | kkkk | C,DC,Z   |       |

| KORLW    | k    | Exclusive OR literal with W | 1             | 11   | 1010   | kkkk  | kkkk | z        |       |

| Byte-oriented file register operations                   |

|----------------------------------------------------------|

| OPCODE d f(FILE #)                                       |

| d = 0 for destination W                                  |

| d = 1 for destination f                                  |

| f = 7-bit file register address                          |

| Bit-oriented file register operations                    |

|                                                          |

| OPCODE b (BIT #) f (FILE #)                              |

| b = 3-bit bit address<br>f = 7-bit file register address |

|                                                          |

| Literal and control operations                           |

| General                                                  |

| 13 8 7 0                                                 |

| OPCODE k (literal)                                       |

| k = 8-bit immediate value                                |

| and and are interview and                                |

| CALL and GOTO instructions only<br>13 11 10 0            |

|                                                          |

| k = 11-bit immediate value                               |

|                                                          |

|                                                          |

|                                                          |

# 1. Copy value from/to file register or literal to/from w

| Mnemonic   | Description                | Status | Function |

|------------|----------------------------|--------|----------|

| movf fr, d | Move file register         | Z      | fr => d  |

| movwf fr   | Move W to file<br>register |        | w => fr  |

| movlw k    | Move literal to W          |        | k => W   |

|            |                            |        |          |

| Move Commands: |                                                    |  |  |  |  |  |

|----------------|----------------------------------------------------|--|--|--|--|--|

| movlw 0xF2     | : stores the number 0xF2 into the W register       |  |  |  |  |  |

| movwf 0x0C     | : stores the W register contents into file H'0C'   |  |  |  |  |  |

| movf 0x0C,w    | : loads the contents of file H'OC' into W register |  |  |  |  |  |

| movf 0x0C,f    | : loads the contents of file H'0C' into file H'0C' |  |  |  |  |  |

|                |                                                    |  |  |  |  |  |

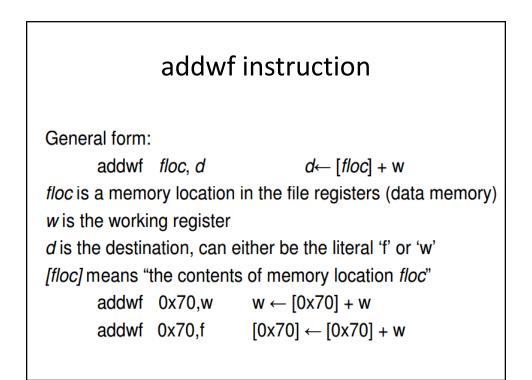

## 2. Logic / arithmetic instructions with a file register and w

| Mnemonic   | Description | Status  | Function      |

|------------|-------------|---------|---------------|

| addwf fr,d | addition    | Z, DC,C | fr + W => d   |

| subwf fr,d | subtraction | Z, DC,C | fr - W => d   |

| andwf fr,d | Logical and | Z       | fr AND W => d |

| iorwf fr,d | Logical or  | Z       | fr OR W => d  |

| xorwf fr,d | xor         | Z       | fr XOR W => d |

|            |             |         |               |

| 3. Logic / arithmetic instructions with |

|-----------------------------------------|

| literal and w                           |

| Mnemonic | Description | Status  | Function     |

|----------|-------------|---------|--------------|

| addlw k  | addition    | Z, DC,C | W + k => W   |

| sublw k  | subtraction | Z, DC,C | W- k => W    |

| andlw k  | Logical and | Z       | W AND k => W |

| iorlw k  | Logical or  | Z       | W OR k => W  |

| xorlw k  | xor         | Z       | W XOR k => W |

|          |             |         |              |

| 4.0        | 4.One operand logic / arithmetic     |        |                                             |  |  |  |  |  |

|------------|--------------------------------------|--------|---------------------------------------------|--|--|--|--|--|

|            | instructi                            | ons    |                                             |  |  |  |  |  |

| Mnemonic   | Description                          | Status | Function                                    |  |  |  |  |  |

| clrw       | Clear accumulator W                  | Z      | 0 => W                                      |  |  |  |  |  |

| clrf fr    | Clear file register fr               | Z      | 0 => fr                                     |  |  |  |  |  |

| decf fr,d  | Decrement file register fr           | Z      | fr - 1 => d                                 |  |  |  |  |  |

| incf fr, d | Increment file register fr           | Z      | fr + 1 => d                                 |  |  |  |  |  |

| comf fr,d  | 1's complement file register fr      | Z      | not fr => d                                 |  |  |  |  |  |

| rlf fr, d  | Rotate file register fr left thru C  | С      | C <= fr(7), fr(i) <= fr(i-1), fr(0) <=<br>C |  |  |  |  |  |

| rrf fr, d  | Rotate file register fr right thru C | С      | C => fr(7), fr(i) => fr(i-1), fr(0) =><br>C |  |  |  |  |  |

| bcf fr, b  | Bit clear on file register fr        |        | 0 => fr(b)                                  |  |  |  |  |  |

| bsf fr, b  | Bit set on file register fr          |        | 1 => fr(b)                                  |  |  |  |  |  |

| swapf fr,d | swap halves of fr                    |        | (fr(0:3) <=> fr(4:7)) => d                  |  |  |  |  |  |

| nop        | No operation                         |        |                                             |  |  |  |  |  |

### Bit Set/Clear Commands

| bcf 0x0C,0<br>bsf 0x0D,3 | : clear the 0th bit of file H'0C'<br>: set the 3rd bit of file H'0D'               |

|--------------------------|------------------------------------------------------------------------------------|

| btfsc 0x42,0             | : test the 0th bit of the file H'42', if it is 0, then skip the next line of code. |

| btfss 0x43,1             | : test the 1st bit of the file H'43', if it is 1, then skip the next line of code. |

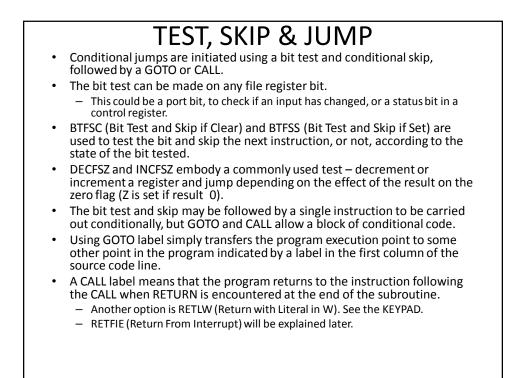

### 5. Branch, Skip and Call instructions

| Mnemonic    | Description                           | Status | Function                          |

|-------------|---------------------------------------|--------|-----------------------------------|

| goto addr   | branch to addr                        |        | addr => PC(0:10)                  |

| call addr   | call routine at addr                  |        | PC => TOS<br>addr => PC(0:10)     |

| decfsz fr,d | Decrement fr, skip if zero            |        | fr - 1 => d, skip if 0            |

| incfsz fr,d | Increment fr, skip next instr if zero |        | fr + 1 => d, skip next instr if 0 |

| btfsc fr,b  | Bit test fr, skip if clear            |        | skip next instr if fr(b) =0       |

| btfss fr,b  | Bit test fr, skip if set              |        | skip next instr if fr(b)=1        |

| return      | return from subroutine                |        | TOS => PC                         |

| retlw k     | return with literal in w              |        | k =>w, TOS => PC                  |

| retfie      | return from interrupt                 |        | TOS => PC, 1 => GIE               |

|             |                                       |        |                                   |

| CONTROL                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>NOP simply does nothing for one instruction cycle<br/>(four clock cycles).</li> </ul>                                                                                                      |

| <ul> <li>very useful for putting short delays in the program</li> </ul>                                                                                                                             |

| <ul> <li>SLEEP stops the program, such that it can be restarted with an external interrupt.</li> </ul>                                                                                              |

| <ul> <li>The unused locations contain the code 3FFF (all 1 s), which is a valid instruction (ADDLW FF).</li> </ul>                                                                                  |

| <ul> <li>CLRWDT means clear the watchdog timer. If the<br/>program gets stuck in a loop or stops for any<br/>other reason, it will be restarted automatically by<br/>the watchdog timer.</li> </ul> |

| <ul> <li>To stop this from happening, the watchdog timer<br/>must be reset at regular intervals of less than,<br/>say, 10 ms, within the program loop, using<br/>CLRWDT.</li> </ul>                 |

|                                                                                                                                                                                                     |

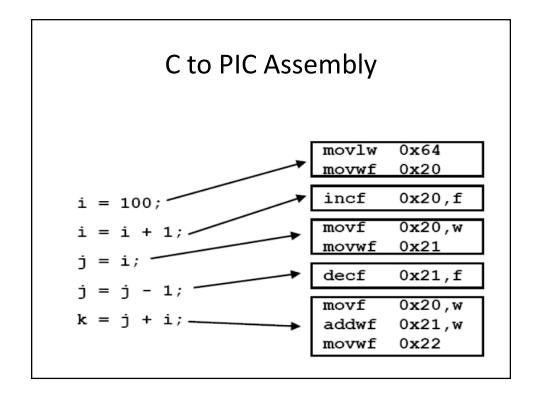

```

INCLUDE "p16f877.inc"

; Register Usage

mptest.asm

CBLOCK 0x020 ;

i, j,k ; reserve space

ENDC

myid equ D'100' ; define myid label

This file can be

org 0

assembled by

movlw myid ; w <- 100

MPLAB into PIC

movwf i ; i <- w;</pre>

machine code and

incf i,f ; i <- i + 1

simulated.

movf i,w ; w <- i

movwf j

; j <- w

Labels used for

memory locations

decf j,f ; j <- j - 1

0x20 (i), 0x21(j),

0x22(k) to increase

movf i,w ; w <- I

code clarity

addwf j,w ; w <- w + j

movwf k ; k <- w

here

goto here

; loop forever

end

```

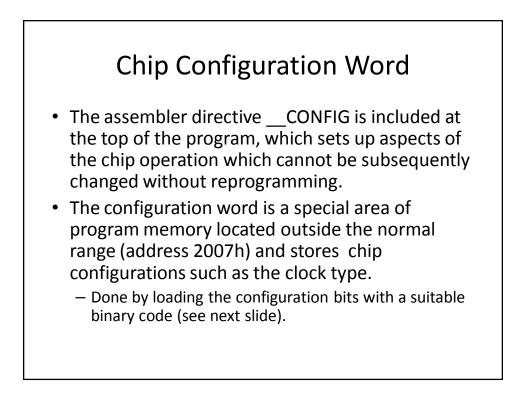

### Chip Configuration Word

| Bit    | Label            | Function                                         | Default | Enabled | Typical |

|--------|------------------|--------------------------------------------------|---------|---------|---------|

| 15     | -                | None                                             | 0       | х       | 0       |

| 14     | -                | None                                             | 0       | х       | 0       |

| 13     | CP1              | Code protection                                  | 1       | 0       | 1       |

| 12     | CP0              | (4 levels)                                       | 1       | 0       | 1       |

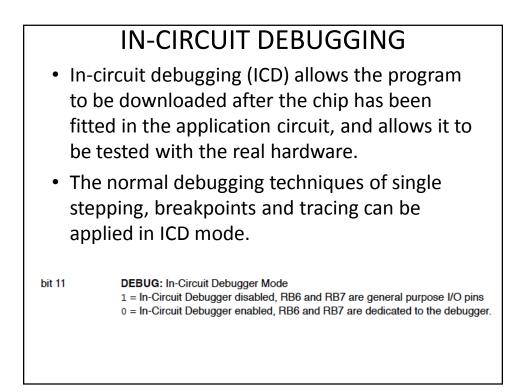

| 11     | DEBUG            | In-circuit debugging (ICD)                       | 1       | 0       | 0       |

| 10     | -                | None                                             | 1       | х       | 1       |

| 9      | WRT              | Program memory write enable                      | 1       | 1       | 1       |

| 8      | CPD              | EEPROM data memory write protect                 | 1       | 0       | 1       |

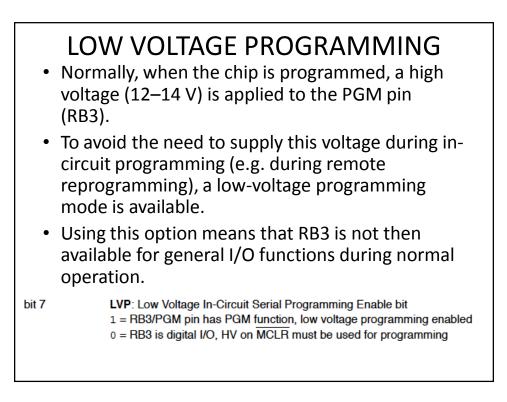

| 7      | LVP              | Low-voltage programming enable                   | 1       | 1       | 0       |

| 6      | BODEN            | Brown-out reset (BoR) enable                     | 1       | 1       | 0       |

| 5      | CP1              | Code protection (CP)                             | 1       | 0       | 1       |

| 4      | CP0              | (repeats)                                        | 1       | 0       | 1       |

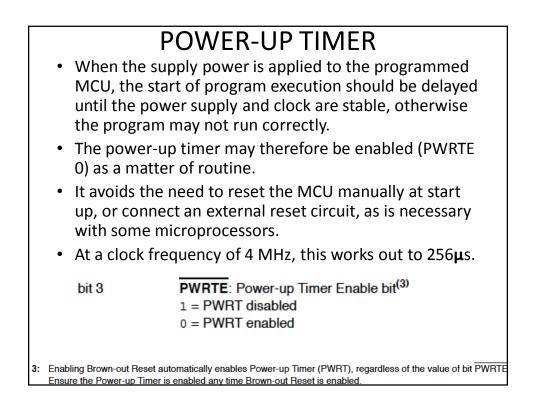

| 3      | PWRTE            | Power-up timer (PuT) enable                      | 1       | 0       | 0       |

| 2      | WDTE             | Watchdog timer (WdT) enable                      | 1       | 1       | 0       |

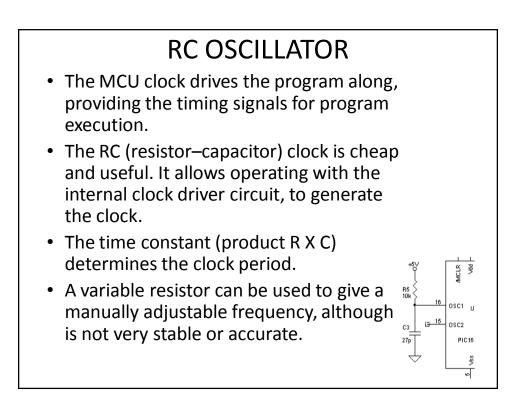

| 1      | FOSC1            | Oscillator type select                           | 1       | x       | 0       |

| 0      | FOSC0            | RC = 11, HS = 10, XT = 01, LP = 00               | 1       | х       | 1       |

| Defau  | ılt = 3FFF (RC c | lock, PuT disabled, WdT enabled).                |         |         |         |

|        |                  | F3 (RC clock, ICD disabled, PuT enabled, WdT dis | abled). |         |         |

| Typica | al XT clock = 37 | 31 (XT clock, ICD enabled, PuT enabled, WdT disa | bled).  |         |         |

|   | CODE PROTECTION                                                                                                                                                                                         |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Normally, the program machine code can be read back to the programming host computer, be disassembled and the original source program recovered.                                                        |

| • | This can be prevented if commercial or security considerations require it. The code protection bits (CP1:CP0) disable reads from selected program areas.                                                |

| • | Program memory may also be written from within the program itself, disabled via the WRT bit.                                                                                                            |

| • | Data EEPROM may also be protected from external reads in the same way via the CPD bit, while internal read and write operations are still allowed, regardless of the state-of-the code protection bits. |

| • | bit 13-12, bit 5-4                                                                                                                                                                                      |

| • | CP1:CP0: FLASH Program Memory Code Protection bit, All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.                                                |

| • | 11 = Code protection off                                                                                                                                                                                |

| • | 10 = 1F00h to 1FFFh code protected                                                                                                                                                                      |

| • | 01 = 1000h to 1FFFh code protected                                                                                                                                                                      |

| • | 00 = 0000h to 1FFFh code protected                                                                                                                                                                      |

|   |                                                                                                                                                                                                         |

|   |                                                                                                                                                                                                         |

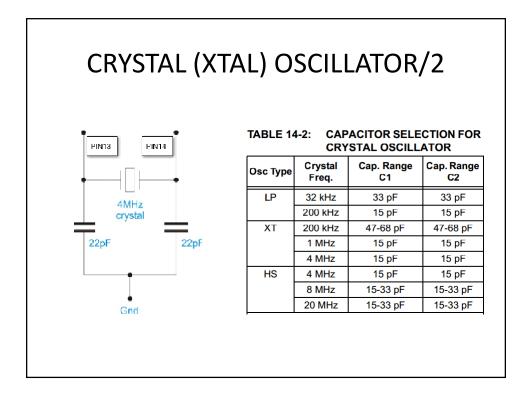

### **CRYSTAL (XTAL) OSCILLATOR**

- Used for greater precision

- uses the hardware timers to make accurate measurements

- generate precise output signals

- Normally, it is connected across the clock pins with a pair of small capacitors (15 pF) to stabilize the frequency.

- The crystal acts as a self-contained resonant circuit, where the quartz or ceramic crystal vibrates at a precise frequency when subject to electrical stimulation.

- A convenient value (used in our examples later) is 4 MHz; this gives an instruction cycle time of 1 μs

- This is the maximum frequency allowed for the XT configuration setting.

- Operating at higher frequency requires the selection of the HS configuration option.

- Each instruction takes four clock cycles

### CONFIGURATION SETTINGS

- The default setting for the configuration bits is 3FFF, which means

- The code protection is off

- In-circuit debugging disabled

- Program write enabled

- Low-voltage programming enabled

- Brown-out reset enabled

- Power-up timer disabled

- Watchdog timer enabled

- RC oscillator selected.

- A typical setting for basic development work would enable in-circuit debugging, enable the power-up timer

This would minimize the possibility of a faulty start-up.

- For reliable starting, disable the watchdog timer and use the XT oscillator type.

- By default, the watchdog timer is enabled.

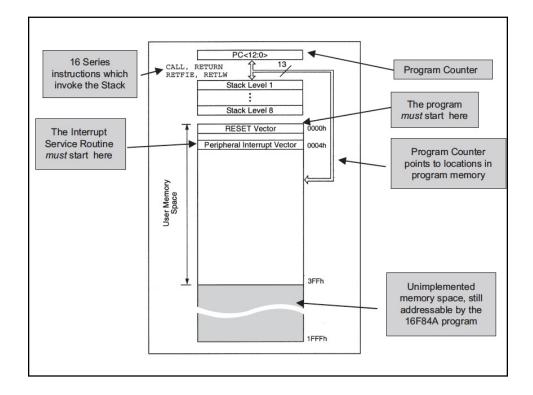

### **SUBROUTINES**

- A label is used at the start of the subroutine

- When a subroutine is called (Using the CALL instruction),

- the destination address is copied into the program counter

- the return address (the one following the CALL) is pushed onto the stack

- In the PIC, there are 8 stack address storage levels, which are used in turn.

- The subroutine is terminated with a RETURN instruction

- causes the program to go back to the original position and continue.

- achieved by popping the address from the top of the stack and replacing it in the program counter.

- CALL and RETURN must always be used in sequence to avoid a stack error, and a possible program crash.

- In the PIC, the stack is not directly accessible

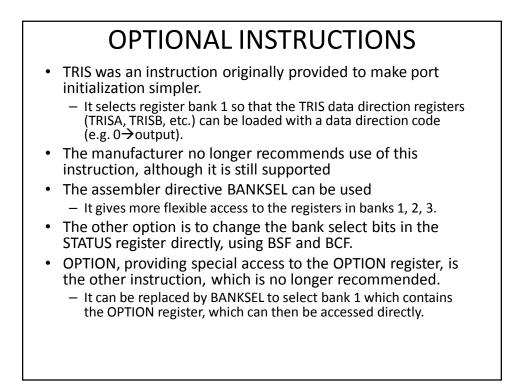

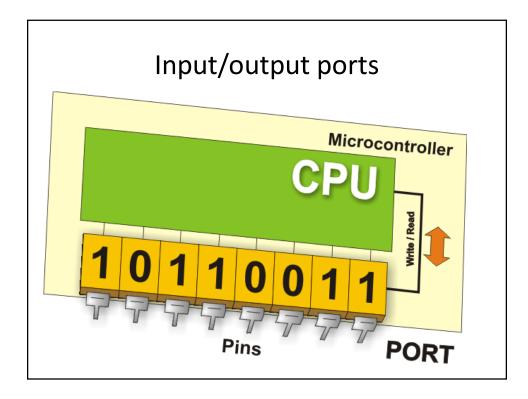

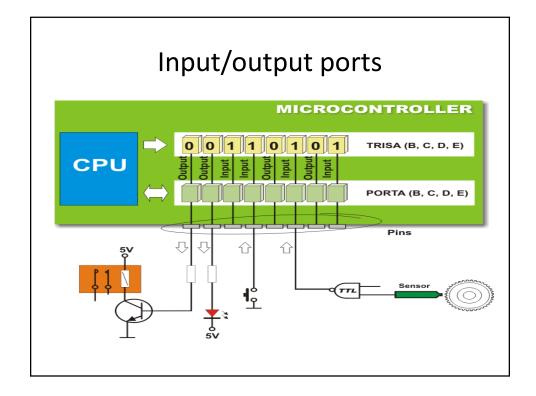

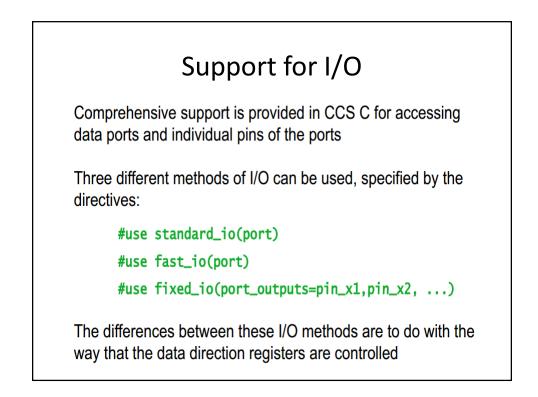

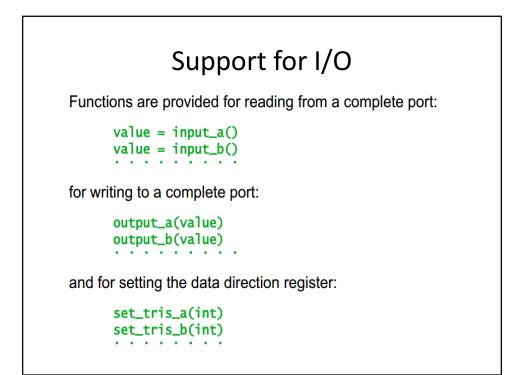

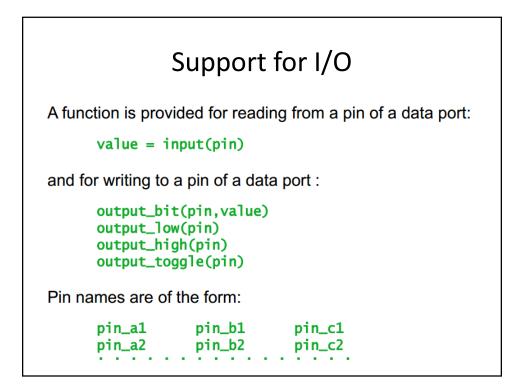

# Input/output ports There are five parallel ports in the PIC 16F877, labelled A-E. All pins can be used as bit- or byte-oriented digital input or output with Some having alternate functions depending on the initialization of the relevant control registers. The TRIS (data direction) register bits in bank 1, default to 1, setting the ports B, C and D as inputs. Ports A and E are set to ANALOGUE INPUT by default, because the analogue control register ADCON1 in bank 1 defaults to 0 - - 0000. To set up these ports for digital I/O, this register must be loaded with the code x - - 011x (x don't care) e g

- be loaded with the code x - 011x (x don't care),e.g. 06h.

- ADCON1 can be initialized with bit codes that give a mixture of analogue and digital I/O on Ports A and E.

- ADCON1 is in bank 1 so BANKSEL is needed to access it.

|        |      | F       | Port functions                                                                                                                    |                            |                   |

|--------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|

|        | Bits | Pins    | Alternate function/s                                                                                                              | Bit                        | Default           |

| Port A | 6    | RA0-RA5 | Analogue inputs<br>Timer0 clock input<br>Serial port slave select input                                                           | 0,1,2,3,5<br>4<br>5        | Analogue<br>Input |

| Port B | 8    | RB0-RB7 | External interrupt<br>Low-voltage programming input<br>Serial programming<br>In-circuit debugging                                 | 0<br>3<br>6,7<br>6,7       | Digital<br>I/O    |

| Port C | 8    | RC0-RC7 | Timer1 clock input/output<br>Capture/Compare/PWM<br>SPI, I <sup>2</sup> C synchronous clock/data<br>USART asynchronous clock/data | 0,1<br>1,2<br>3,4,5<br>6,7 | Digital<br>I/O    |

| Port D | 8    | RD0-RD7 | Parallel slave port data I/O                                                                                                      | 0–7                        | Digital<br>I/O    |

| Port E | 3    | RE0-RE2 | Analogue inputs<br>Parallel slave port control bits                                                                               | 0,1,2<br>0,1,2             | Analogue<br>Input |

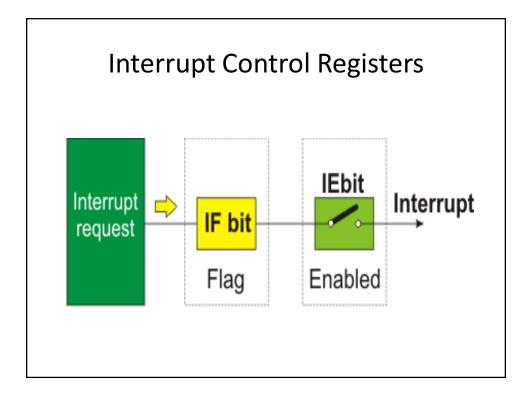

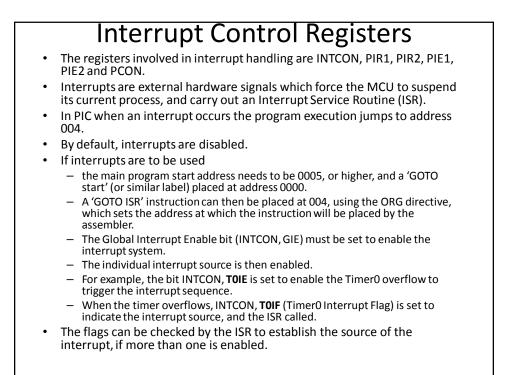

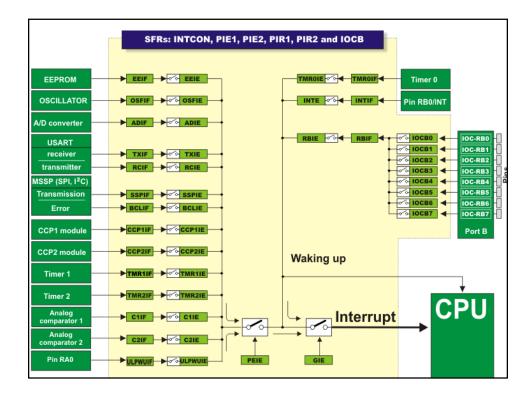

| INTERRUPTS                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>The stack is used when an interrupt is processed.</li> </ul>                                                                                                                           |

| <ul> <li>An interrupt is effectively a call and return which is initiated by an<br/>external hardware signal</li> </ul>                                                                         |

| <ul> <li>Forces the processor to jump to a dedicated instruction sequence,<br/>an Interrupt Service Routine (ISR).</li> </ul>                                                                   |

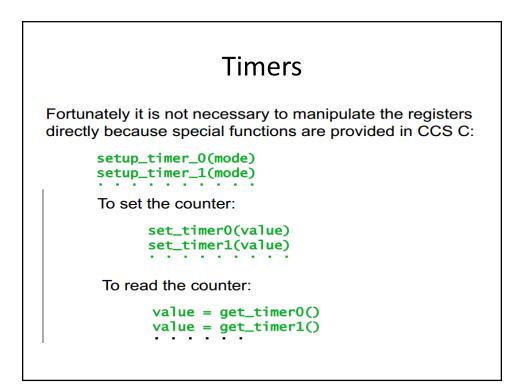

| <ul> <li>For example, the MCU can be set up so that when a hardware timer<br/>times out (finishes its count), the process required at that time is<br/>called via a timer interrupt.</li> </ul> |

| When an interrupt signal is received,                                                                                                                                                           |

| <ul> <li>the current instruction is completed and</li> </ul>                                                                                                                                    |

| <ul> <li>the address of the next instruction (the return address) is pushed into<br/>the first available stack location.</li> </ul>                                                             |

| <ul> <li>The ISR is called</li> </ul>                                                                                                                                                           |

| <ul> <li>The ISR is terminated with the instruction RETFIE (return from<br/>interrupt), which causes the return address to be pulled from the<br/>stack.</li> </ul>                             |

| <ul> <li>Program execution then restarts at the original location.</li> </ul>                                                                                                                   |

| <ul> <li>If necessary, the registers must be saved at the beginning of the ISR,<br/>and restored at the end, in spare set of file registers.</li> </ul>                                         |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

| Inte                        | rrupt so                             | ources                               | and control bits                                                                                                                                                               |

|-----------------------------|--------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Source                      | Enable<br>Bit Set                    | Flag<br>Bit Set                      | Interrupt Trigger Event                                                                                                                                                        |

| TMR0<br>RB0<br>RB4-7        | INTCON,5<br>INTCON,4<br>INTCON,3     | INTCON,2<br>INTCON,1<br>INTCON,0     | Timer0 count overflowed<br>RB0 input changed (also uses INTEDG)<br>Port B high nibble input changed                                                                            |

| Peripherals                 | INTCON,6                             |                                      |                                                                                                                                                                                |

| TMR1<br>TMR2<br>CCP1<br>SSP | PIE1,0<br>PIE1,1<br>PIE1,2<br>PIE1,3 | PIR1,0<br>PIR1,1<br>PIR1,2<br>PIR1,3 | Timer1 count overflowed<br>Timer2 count matched period register PR2<br>Timer1 count captured in or matched CCPR1<br>Data transmitted or received in<br>Synchronous Serial Port |

| ТХ                          | PIE1,4                               | PIR1,4                               | Transmit buffer empty in Asynchronous<br>Serial Port                                                                                                                           |

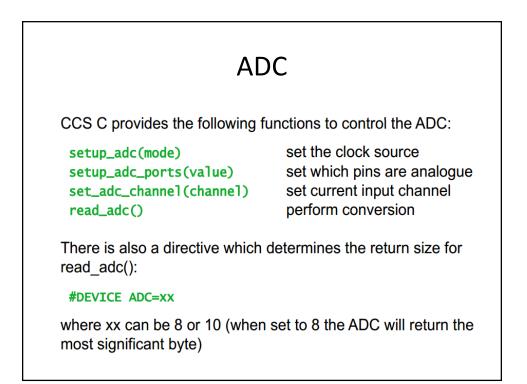

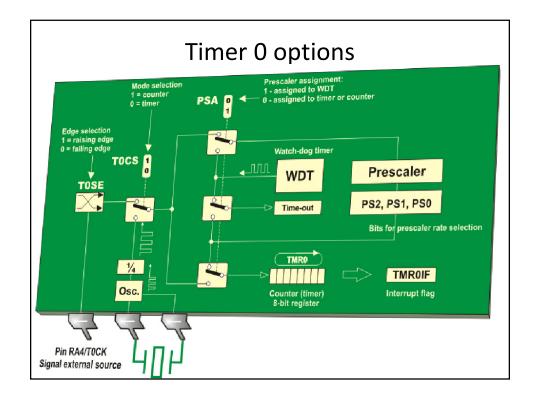

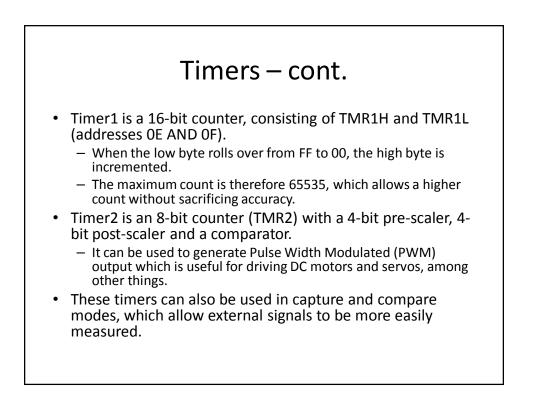

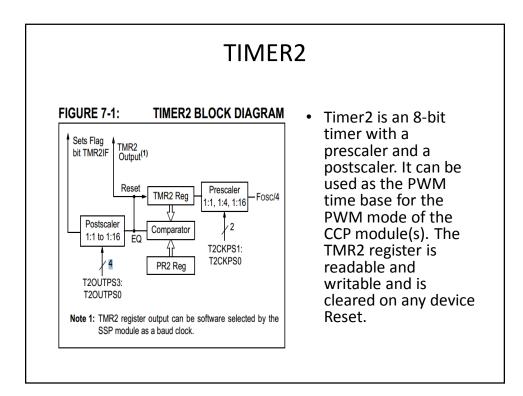

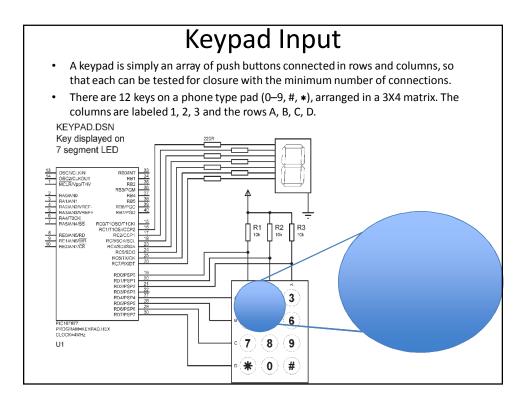

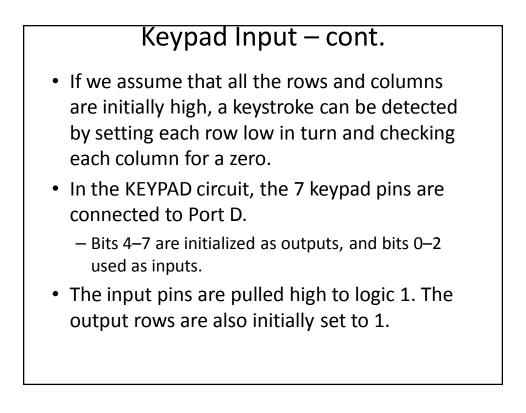

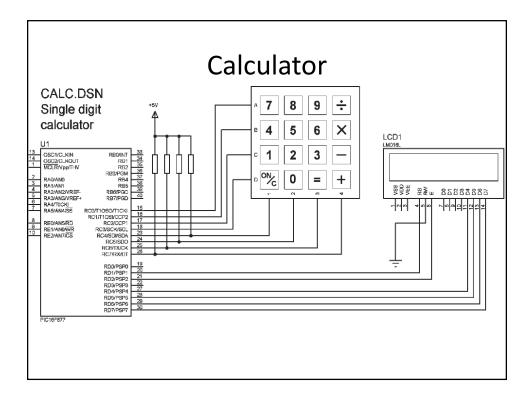

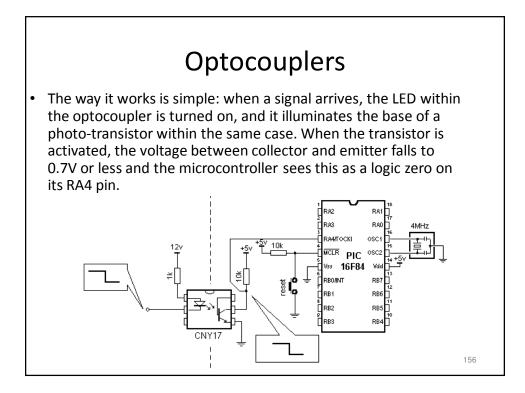

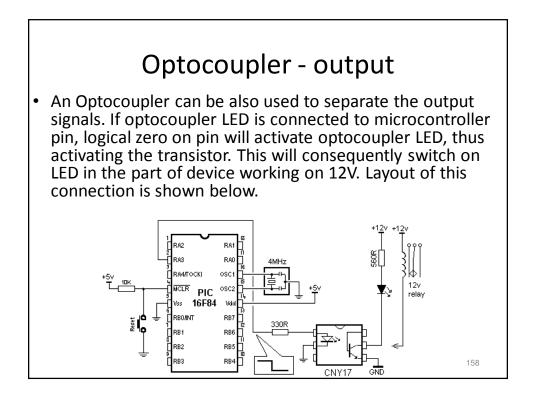

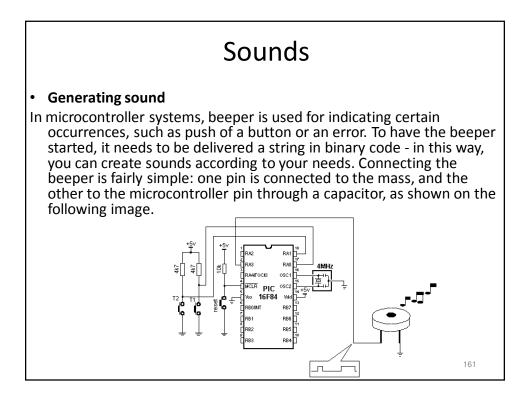

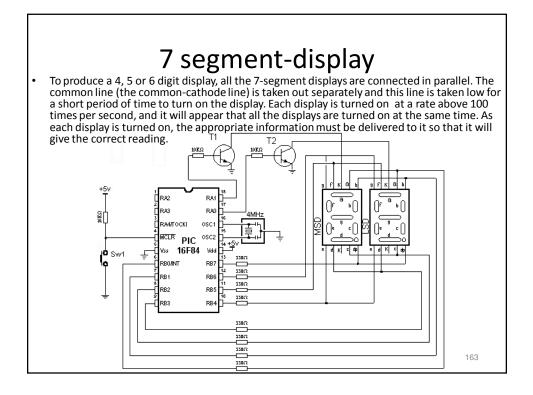

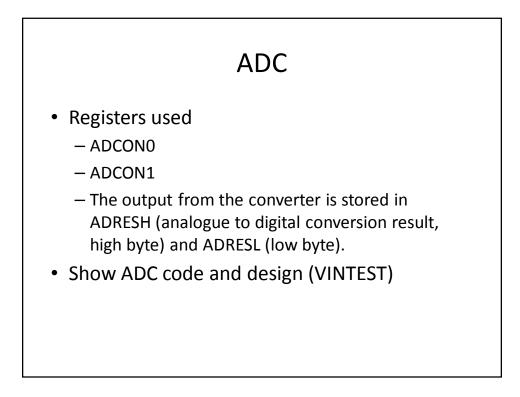

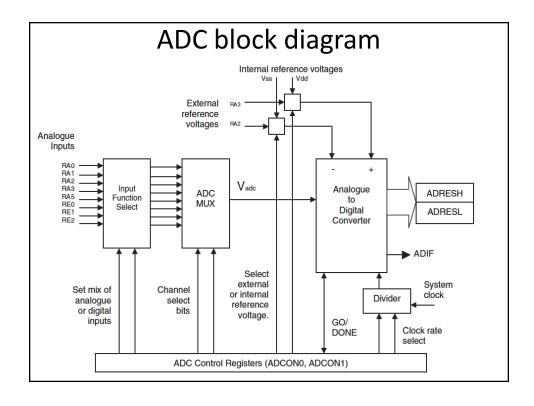

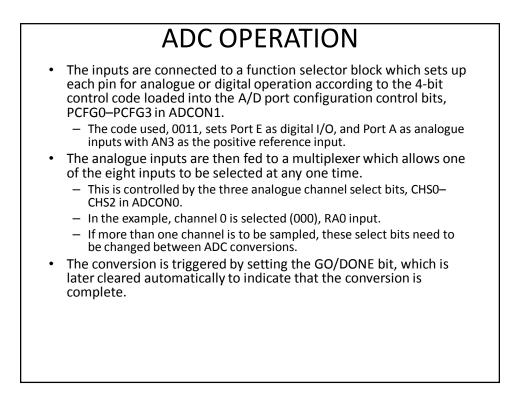

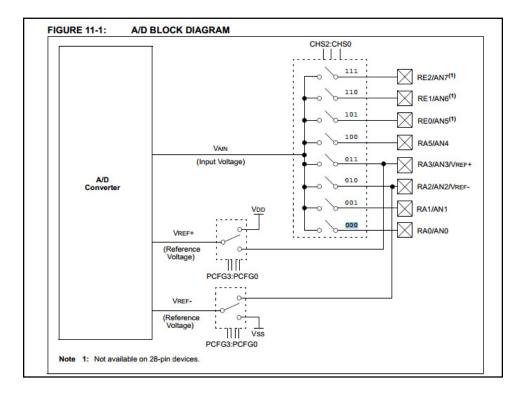

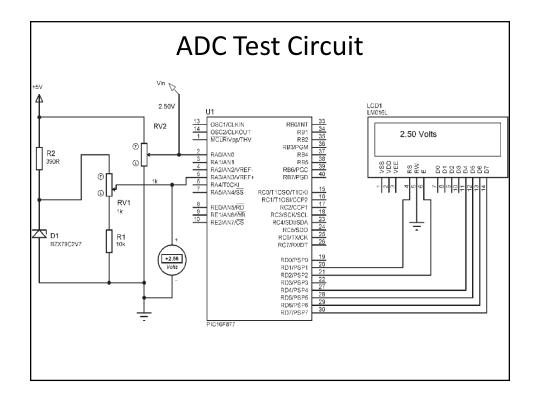

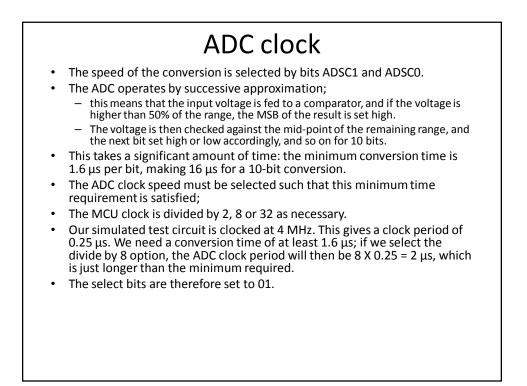

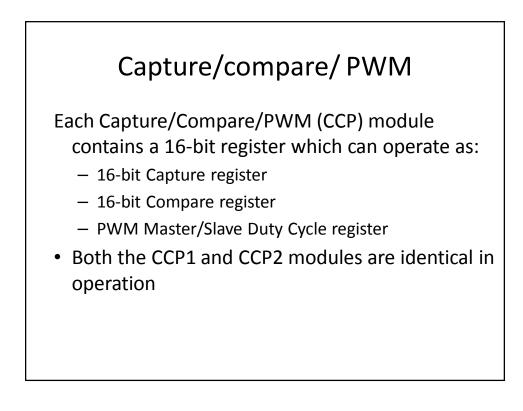

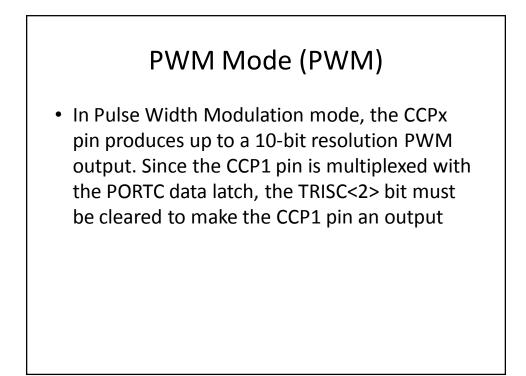

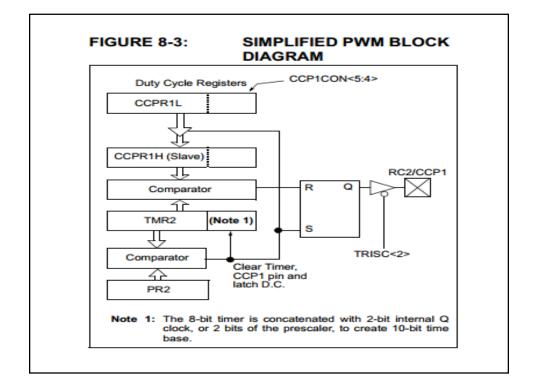

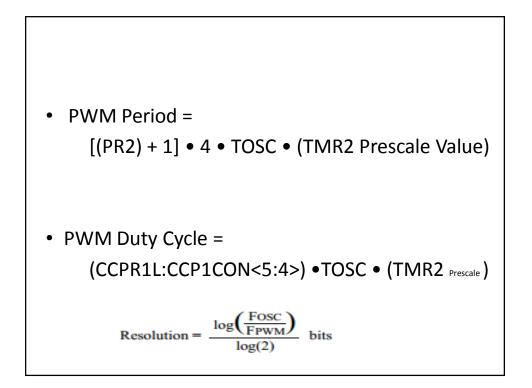

| RC                          | PIE1,5                               | PIR1,5                               | Receive buffer full in Asynchronous<br>Serial Port                                                                                                                             |