#### ENCS336 - Second Exam

2<sup>nd</sup> Semester 08/09 Date: May 14<sup>th</sup>, 2009

| Student ID :_   |                     |

|-----------------|---------------------|

| Student Name: _ | _typical solutions  |

| Section 1       | Abdel Salam Sayyad  |

| Section 2       | Mohammad Abu Ayyash |

| Section 3       | Mahmoud Qasrawi     |

## **Instructions:**

- You have 80 minutes to answer all questions, so budget your time carefully!

- Turn OFF your mobile

- To make sure you receive credit, please write clearly and show your work

| Question | Maximum | Your Score |

|----------|---------|------------|

| 1        | 24      | 24         |

| 2        | 36      | 36         |

| 3        | 16      | 16         |

| 4        | 12      | 12         |

| 5        | 12      | 12         |

| Total    | 100%    | 100%       |

|    | True | False |                                                                                                                                           |

|----|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| a) | O    | O     | DRAM is more popular than SRAM because it can be accessed faster than SRAM.                                                               |

| b) | O    | O     | To properly handle an external interrupt, the current instruction must be suspended then restarted.                                       |

| c) | O    | O     | Larger caches have better hit rates but longer latency.                                                                                   |

| d) | O    | O     | Multi-level caches generally operate by checking the smallest Level 1 (L1) cache first; if it hits, the processor proceeds at high speed. |

| e) | О    | Ο     | Increasing the disk size will increase the average seek time.                                                                             |

| f) | О    | О     | Programmable ROM types (PROM, EPROM, EEPROM, and Flash) are all written (programmed) using electricity.                                   |

| g) | O    | O     | Both DRAM and EPROM are volatile memory.                                                                                                  |

| h) | O    | O     | The refresh cycle in SRAM causes slow access to data.                                                                                     |

| i) | О    | О     | In interrupt-driven I/O the CPU has to check the status register periodically to know if the operation is accomplished.                   |

| j) | O    | 0     | It is possible to interrupt an interrupt service routine (ISR).                                                                           |

| k) | O    | O     | Cache memory is implemented using EPROM technology.                                                                                       |

| 1) | О    | O     | SRAM consume more power than DRAM.                                                                                                        |

#### Question 2: Choose the right answer (36 marks)

1. A disk drive has 3 double-sided platters. The drive has 300 cylinders. How many tracks are there?

A. 600

B. 900

C. 1800

D. 3600

E. 300

### 2. Cache memory refers to

- A. cheap memory that can be plugged into the mother board to expand main memory

- B. fast memory typically present on the processor chip that is used to store recently accessed data

- C. a reserved portion of main memory used to save important data

- D. a special area of memory on the chip that is used to save frequently used constants

- E. Stack memory

- 3. Which one has the fastest access time?

- A. Magnetic tape

- B. Magnetic disk

- C. Main memory

- D. Cache

- E. Flash disk

- 4. Usually, cache memory is:

- A. small SRAM

- B. Large SRAM

- C. small DRAM

- D. SDRAM

- E. DRAM

- 5. One of the following is not true:

- A. Both Static RAM and Dynamic RAM don't save data if the power shut down

- B. Both Static RAM and Dynamic RAM must have refreshing circuit,

- C. Static RAM is more expensive (per bit) because a latch/flip-flop takes more space than a capacitor/transistor.

- D. Static RAM is faster than dynamic RAM

- E. Typically, DRAM is used as main memory in computer system, while Static RAM is used in cache.

- 6. Consider a 256K x 1-bit SRAM chip. The memory module is organized as rows and columns. How many address lines are needed?

- A. 8

- B. 9

- C. 18

- D. 256

- E. 512

| <ul> <li>7. How many 256K X 8 DRAM modules are needed to implement 1M X 16 DRAM module?</li> <li>A. 2</li> <li>B. 4</li> <li>C. 8</li> <li>D. 16</li> <li>E. It is not possible , we only can implement it using 256K X 16 modules</li> </ul>                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>8. A system uses memory-isolated I/O addressing mode, if there are 8 address lines, then the system can support up to: <ul> <li>A. 8 memory locations , and 8 I/O locations</li> <li>B. Total 512 memory and I/O locations</li> <li>C. Total 256 memory and I/O locations</li> <li>D. 512 memory locations , and 512 I/O locations</li> <li>E. 256 memory locations , and 256 I/O locations</li> </ul> </li> </ul>                                                                                                     |

| <ul> <li>9. The of a disk is the time needed to position the read/write head over the correct track.</li> <li>A. Rotationally delay</li> <li>B. transfer speed</li> <li>C. frequency</li> <li>D. Access time</li> <li>E. Seek time</li> </ul>                                                                                                                                                                                                                                                                                   |

| <ul> <li>10. A disk with spindle speed =7500 rpm. Average seek time = 4.5ms, 512-byte sectors. What is the maximum rotational delay?</li> <li>A. 8ms</li> <li>B. 4ms</li> <li>C. 4.5ms</li> <li>D. 0.13ms</li> <li>E. 0.26ms</li> </ul>                                                                                                                                                                                                                                                                                         |

| <ul> <li>11. One of the following is not true: <ul> <li>A. The direct mapped cache is the simplest form of cache and the easiest to check for a hit</li> <li>B. The fully associative cache has the best hit ratio</li> <li>C. The fully associative cache suffers from problem of involving searching the cache</li> <li>D. In N-way set associative cache, Hit ratio increase as N Increases</li> <li>E. Direct mapped, fully associative and set associative caches need block replacement algorithms</li> </ul> </li> </ul> |

| 12. A system uses direct-mapped cache. Imagine the processor needs 3 different addresses (call them X, Y and Z) in the following sequence (X, Y, X, Y, Z, X, Y, Y, Y, Z). Suppose both X and Y map to the cache line 0, Z maps to cache line 3. The hit ratio is:  A. 0.30  B. 0.70  C. 0.50  D. 0.20  E. 0.90                                                                                                                                                                                                                  |

| Score |  |

|-------|--|

|-------|--|

#### Question 3: (16 marks)

Consider a **Seagate Barracuda** hard disk with the following parameters:

- Number of sectors per track = 600 sectors

- Number of bytes per sector = 512 bytes

- Number of tracks per one platter = 29851 tracks

- Number of platters = 2 single-sided platters

- Spindle speed = 7200 rpm

- Average seek time = 9.5 ms

- **1.** What is the number of cylinders in this hard disk?

[2 marks]

# of cylinders = # of tracks = 29851 cylinders

**2.** What is the number of tracks per one cylinder?

[2 marks]

Number of tracks per one cylinder = number of platters = 2

3. What is the total capacity of the hard disk?

[4 marks]

```

Capacity = # of platters * # of tracks/platter * # of sectors/ track * # of bytes/sector

= 2 * 29851 * 600 * 512

= 18340454400 bytes

```

4. What is the average rotational delay?

[4 marks]

```

Average rotational delay = 1/2r = 1/2 (7200/60) = 4.17 ms

```

5. What is the total time needed to read data of 10 Kbytes stored on 20 adjacent sectors?

[4 marks]

```

= seek time + Rotational delay + transfer time

= 9.5 ms + 4.17 ms + b/rN

= 9.5 ms + 4.17 ms + (10 * 1024)/ (7200/60) * (600 * 512)

= 9.5 ms + 4.17 ms + 0.3 ms

= 13.97 ms

```

No partial marks.

| Score |  |

|-------|--|

|-------|--|

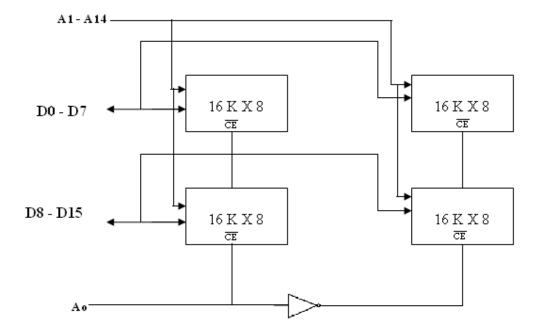

#### **Question 4: (12 marks)**

Consider a 16-bit processor that requires 64 Kbytes main memory. Design a memory module for the processor using only 16-Kbyte memory chips organized as 16K X 8 bit.

#### **Solution:**

- Memory locations = 32 K locations, 15 address lines are needed (A0 A15)

- Available chips 16 Kbytes (16K X 8), we need 4 chips, each needs 14 address lines

- 2 marks for # chips = 4

- 4 marks for connecting 14 address lines to all chips

- 4 marks for connecting the data lines correctly

- 2 marks for decoding one address bit to drive chip selects.

- No partial marks.

Score

#### **Question 5: (12 marks)**

Consider a computer system with the following characteristics:

- **1.** 16-Mbyte main memory,

- 2. 256-Kbyte cache memory,

- **3.** Byte Addressable,

- **4.** 8 bytes per cache line.

Suppose that the cache memory is to be mapped as 4-way set associative.

a. How many lines are there in the cache memory?

b. How many sets are there in the cache memory?

```

# Sets = (32 * 1024 lines) / (4 lines/set) = 8 * 1024 = 8192 sets [3 marks]

```

c. How many blocks are there in main memory?

```

# Blocks = (16 MBytes) / (8 Bytes/block) = 2 M blocks [3 marks]

```

d. How long (in bits) is the Tag field?

```

Total memory address bits = log_2 (16M) = 24 bits

Set bits = log_2 (8192) = 13 bits

Word bits = log_2 (8) = 3 bits

```

Tag bits = total bits - set bits - word bits = 24 - 13 - 3 = 8 bits [3 marks]

No partial marks.

# Computer Systems Engineering Department Computer Organization – ENCS238 Second Exam

|    | Name:                                                                                                                                                         | 1                               | ID:                  | Section: 1 2 3                    |        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|-----------------------------------|--------|

|    |                                                                                                                                                               | 3                               |                      |                                   |        |

|    | Question 1: [30] (Multiple choic                                                                                                                              | e; 2 pts each)                  |                      |                                   |        |

| 1. | CPU checks for an interrupt sign (A) Starting of last Machine cycle (B) During execution cycle (C) Operand Fetch cycle (D) Instruction fetch cycle            |                                 |                      |                                   |        |

| 2. | In 8086 the Overflow flag is set of (A) the sum is more than 16 bits (B) Signed numbers go out of the (C) Carry and sign flags are set (D) During subtraction |                                 | n arithmetic opera   | ion                               |        |

| 3. | Which of the following is an ille (A) MOV AX, 25000 (C) AND BX, CX                                                                                            | (B) DEC                         | C AL<br>OV DS, 7000H |                                   |        |

| 4. | In a 16-bit floating point format the binary number 101.100×2 <sup>3</sup> (A) 34 (C) 36                                                                      | (B) 5<br>(D) 67                 | onent, and 9-bits m  | antissa, the value of the exponer | nt for |

| 5. | Which of the following variables                                                                                                                              | \ /                             | amount of RAM:       |                                   |        |

|    | (A) x db 255<br>(C) z dw 50 dup(0)                                                                                                                            | (B) y db 80 du<br>(D) small dd  | up('Z')              |                                   |        |

| 6. | The result of mov al, 65 is to stor<br>(A) 0100 0010 in al<br>(C) store 42H in al                                                                             | (B) ASCII cod<br>(D) store 1000 |                      |                                   |        |

| 7.  | The effect of the following instructions push ax add ax, 4                                                  |                                                                                                                       |

|-----|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|     | pop bx mov cx, ax push bx pop ax                                                                            |                                                                                                                       |

|     | on the ax register is  (A) leave it with its original value (C) clear it                                    | (B) add 4 to it (D) double it                                                                                         |

| 3.  | To copy the hexadecimal number A to (A) mov 0bh, ah (C) mov bh, ah                                          | the bh register you write  (B) mov bh, 0ah  (D) mov bh, [ah]                                                          |

| 9.  | Given that all contains the ASCII code (A) add al,32 (C) or al, 1101 1111                                   | of an <u>uppercase</u> letter, it can be converted to lowercase by <b>(B)</b> sub al, 32 <b>(D)</b> and al, 0010 0000 |

| 10. | The word size of an 8086 processor is (A) 8 bits (C) 32 bits                                                | (B) 16 bits<br>(D) 64 bits                                                                                            |

| 11. | One of the following instruction is illeg (A) mov al,[bx] (C) inc [bx]                                      | (B) mov [bx],[2000]<br>(D) add cx,[200]                                                                               |

|     | A computer system has 64MB of memory (A) 24 bit (C) 26 bit Which register will be affected by the in (A) BX | ory (Byte addressable), the minimum size of MAR  (B) 8 bit  (D) 16 bit  Instruction MUL BX  (B) AX                    |

| l4. | (C) DX  The bp register is typically used for acc (A) strings C stack                                       | (D) Both AX and DX ressing (B) memory (D) data segment                                                                |

| 1 1 | Jan. | 2 | 3 | 4   | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|-----|------|---|---|-----|---|---|---|---|---|----|----|----|----|----|----|

| F   |      | B | D | C . | D | B | Α | B | A | B  | B  | Ø. | D  | C  | X  |

## **Question 2:** [15]

Consider a 16-bit floating-point format given in Figure below:

Significant (8 bit) Sign (1 bit) Exponent (7 bit)

a) What is the absolute maximum and absolute minimum normalized numbers that can be represented in this floating-point format? C5PT33

Bias = 2-1 = 03 max  $\frac{126}{126}$ ,  $\frac{126}{126}$ ,  $\frac{126}{126}$ ,  $\frac{126}{126}$  =  $\frac{126}{126$

b) Let  $A = (BD70)_H$  and  $B = (42C8)_H$  are two floating-point numbers, expressed in hexadecimal. Let C = A + B, find the representation of C in 16-bit format given in figure above (show how the floating point calculations are

3

performed step by step) (10 13 les = 63

A = [011 11 01, 0111 0000]

exp. sig. exp. 66-63 = 3 exp. = 61-63 = -2

A = - 1.0111 X2

$A = -0.0000101111X^{3}$

B= 01000010 11001000 B= 0+1.11001 X2

C= +1.10/1/11001 X2 sign = 0  $exp = 3 + 63 = 66 = (1000010)_2$ Sig. = 10111110 in 16-bit Floating-point C = 01000010 10111100 or pounded to

4 2 B E

4 2 BDH C = (42 BE)

# Question 3:[15]

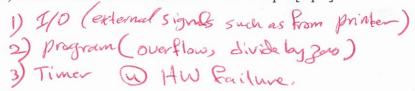

a) What is interrupt? [2pts]

Mechanism by which other Modules (e.g I/O) may interrupt normal sequence of processing to improve process efficiency.

b) Mention three sources that cause an interrupt? [3 pts]

c) Consider a system with five I/O devices: D1, D2, D3, D4 and D5. Interrupts from D1 and D2 has the same priority = 2, D3 has priority = 4, and D4 has priority = 7, and D5 has priority = 5. A user program begins at time t = 0: main mag.

0->10 - at t = 10 D2 interrupt occurs and it needs 20 sec to be handled 10 → 15 D2

- at t = 15 D4 interrupt occurs and it needs 15 sec to be handled 15 -30 DY - at t = 20 D1 interrupt occurs and it needs 10 sec to be handled

30 → 40 D5 40 → 65 D2 - at t = 25 D3 interrupt occurs and it needs 25 sec to be handled

- at t = 30 D5 interrupt occurs and it needs 10 sec to be handled 65 -> 80

Using nested multiple interrupts, complete the table below: [10pts] 20 -> 90 Di

| Device | Interrupt handling start time | Interrupt handling complete |

|--------|-------------------------------|-----------------------------|

| D1     | t= 80                         | 7=90                        |

| D2     | t=10                          | t=80                        |

| D3     | t= 40                         | t=65                        |

| D4     | t=15                          | +=30                        |

| D5     | t=30                          | t=40                        |

# **Question 4:** [20]

a) Identify the operand addressing mode used in each of these instructions: [5 pts]

1) AND DX, AX Register Advessing Mode. (AM)

2) JMP TABLE[BX] Based A.M. (mem. Reg. Indirect)

3) ADD DX,15 Jumediale A.M.

4) CMP WORD PTR [BX+DI], 10 Basel - Indexed A.M. (mem. Indired)

5) MOV IVAL[DI+4],CX Indexed with displacement A.M. (mem. Indired)

b) Assume (all values are in hex) [15 pts]

AX=0000 BX=00050 CX=0003 DX=0000 SI=0050 DI=0000 CS=2000 SS=4000 DS=5000 ES=2000 SP=3000 BP=00050 IP=100

mov cx,7

L: Inc DI

Loop L; if cx != 0 then dec cx and goto L

or AX,[BX+2]

Lea DX,[SI]

POP SI

get 16 bit then Inc SP by two

| 42FFF | 12 |

|-------|----|

| 43000 | 34 |

| 43001 | 56 |

| 43002 | 78 |

|       |    |

| 5004F | AA |

| 50050 | BB |

| 50051 | CC |

| 50052 | DD |

|       |    |

|       |    |

i) What is the physical address of the next instruction to be executed? [2pts]

CS x 10h+ IP = 20100H

ii) What is the lowest possible address of the stack segment? [2pts]

Lowest address when SP = FFFFH

So, lowed physical addess = SSXION + FFFFH & MFFFFF

highest address when offsel = FFFFH. Highest physical address = DS \*10h + FFFF = 5FFFFH

iv) What is the SP and SS after the two instructions push AX push BX: [2pts]  $SP = SP - Y \Rightarrow SP = 2FFCH$

SP = 2 FFCH

SS = YOOOH

address

v) What is the physical address of the source operand of the fourth instruction? [2pts]

DS\*10h+BX+1 = 50000 + 0050+1 = 50051 H

vi) What is the new value of the affected registers after executing these instructions? [5pts]

DX = 0050H

SI=3412H

AX = DDCC H

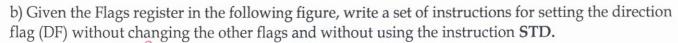

# Question 5: [20]

a) Show how the AL and Flags are affected by

Mov AL, OBBH ADD AL, OCCH

AL= 87H

CF= \ OF= O

ZF= ()

SF=

c) What will be the value in AX after executing the following instructions? Give the answer in both hexadecimal and binary.

mov al, 15 mov ah, 15 xor al, al -> AL= 0 mov cl, 3 shr ax, cl add al, 90h adc ah, 0

AX=(00000000000000

d) What will be the value in AX after executing the following instructions? Assume that DS and ES are set up appropriately to access the variable 'Array'. Give the answer in hexadecimal:

Byte Array dw

1 0 3 2 5 4 7 6 11 11h, 22 22h, 33 33h, 44 44h

mov bx, 1

mov si, 6

mov ax, Array[bx][si-2]

Array

0 11 HSB LSB

# **Birzeit University**

# Computer Systems Engineering Department Computer Organization- ENCS 238 First Exam, May, 6, 2010 2<sup>nd</sup> semester, 2009/2010

(2 hours)

Section 1: Abdalkarim Awad Section 2: Mohammad Abu- Ayyash Section 3: Aziz Qaroush

# Part One (True or False) (20Marks):

| 1  | Given Ax=FFEE BX=7777 the instructions cmp AX, BX followed by JGE L1 will change the IP | F  |

|----|-----------------------------------------------------------------------------------------|----|

|    | to the value associated with L1 (i.e go to L1)                                          |    |

| 2  | Hit ratio measures the expected probability of data being found in main memory.         | F  |

| 3  | Write-through cache reduces the number of write operations to main memory               | F  |

| 4  | Direct mapped, fully associative and set associative caches need block replacement      | F  |

|    | algorithms                                                                              |    |

| 5  | In the LRU (Least Recently Used) replacement algorithm, the data that has been in cache | F  |

|    | memory the longest time is replaced.                                                    |    |

| 6  | The access method used in EPROM is the Random Access                                    | T  |

| 7  | add AL, [2000] is illegal 8086 instruction                                              | F  |

| 8  | The instruction mul Al, 20H is illegal 8086 instruction                                 | T  |

| 9  | Both DRAM and SRAM need refresh                                                         | F  |

| 10 | The instruction Mov AX,[DX] is a legal 8086 instruction                                 | F* |

<sup>\*</sup> DX, AX and CX can't be used as pointers to the data segment. We can us BX (i.e. Mov Ax,[BX] is legal)

## Part Two (Assembly): (35 Marks)

- 1. Assembly languages are difficult for many reasons such as difficult to read, very difficult to debug, ....

But still it has many advantages over high level languages. Give three of these advantages. (5 Marks)

- 1 Assembly program size is smaller than high level languages

- 2 Programs in assembly language will be executed faster than program in high level languages

- 3 It access the hardware more efficient.

- 2. Write a complete assembly program that reads a key from the keyboard and if this key is a number then print on the screen the messages "A number has been pressed" else it print the messages "a non-number has been pressed". You may need the following information (10Marks)

.model small

.stack 100

.data

m1 db " A number has been pressed\$"

m2 db " A non- number has been pressed\$"

.code

mov ax,@data

mov ds,ax

mov ah,1 int 21h

cmp al,"0" jb notnumber cmp al,"9" ja notnumber

lea dx,m1 mov ah,9

int 21h

jmp exit1

notnumber:

lea dx,m2

mov ah,9

int 21h

exit1:

mov ah,4ch

int 21h

end

- ASCII codes for digits 0-9 are 30H-39H

- For display use service 6H (i.e., AH=6H) of Int 21h (DOS interrupt), where the value to be displayed is placed in DL. Or service 2H (i.e., AH=2H) where the value to be displayed is placed in DL. And service 1H to read from the keyboard where the ASCII value of the inserted key will be in AL.

3. Assume(all values are in hex) (10 Marks)

AX=0000 BX=00050 CX=0003 DX=0000 SI=0050 DI=0000 CS=2000 SS=4000 DS=5000 ES=2000 SP=3000 BP=00050 IP=100

| Mov cx,7    |   |

|-------------|---|

| L:          |   |

| Inc DI      |   |

| Loop L      |   |

| or AX,[BX]  | ; |

| Lea DX,[SI] | ; |

| POP SI      |   |

| 42FFF | 12 |

|-------|----|

| 43000 | 34 |

| 43001 | 56 |

| 43002 | 78 |

|       |    |

| 5004F | AA |

|-------|----|

| 50050 | BB |

| 50051 | CC |

| 50052 | DD |

| •••   |    |

a. What is the physical address of the next instruction to be executed?

```

CS*10+IP

20000 +100=20100

```

b. What is the physical address of the source operand of the fourth instruction?

```

DS*10+BX

50000+50=50050

```

c. What is the new value of the affected registers after executing these instructions?

```

AX: CCBB CX:0000 DX:0050 SI:5634 DI:0007 SP:3002 IP:N/A

```

d. What is the physical address of the sources operand in the instruction mov DX,[BP+5]

```

SS*10+BP+5

40000+50+5=40055

```

Note that **SP & BP are two pointers associated with SS**. SP points to the top of stack, and BP points to any location we required in stack segment.

e. What is the SP and SS after the two instructions push AX push BX

```

SS:4000 SP 2FFE

```

4. Show how the AL and Flags are affected by

(5 Marks)

5. Conditional jump (i.e JZ , JNZ...) allow relative range of only +127/-128 bytes form their current location. Knowing that unconditional jump does not have this limitation, show how to implement JZ L1 where L1 is located out side the +127/-128 range? (5 Marks)

## Part Three (Cache & Internal Memory): (45 Marks)

- 1. What is the performance advantage of using a write-back cache over a write-through cache? (4Marks)

- 2. Assume that we have 32-bit processor and it is byte-addressed (i.e. addresses specify bytes). Suppose that it has two way set-associative 512-byte cache, (16 bytes) cache lines (blocks), and uses LRU replacement.

- a. Split the 32-bit address into "tag", "set", and "word" pieces. Which address bits comprise each piece? (6 Marks)

# of words in each line = 16, need 4 bits to represent the word

# of lines = 512/16 = 32 lines

# of sets = # of lines/2 = 16, needs 4 bits to represent the set

The remaining bits of 32 bits used to represent Tag which is 32-4-4 = 24 bits

| TAG: 24 bits | SET: 4 bits | w: 4 bits |

|--------------|-------------|-----------|

|              |             |           |

b. How many sets does this cache have? Explain.

(3Marks)

c. Below is a series of memory read references set to the cache from part (a). Assume that the cache is initially empty and classify each memory references as a hit or a miss. Hint: start by splitting the address into components.

| Address | Set Number  | Hit/Miss? |

|---------|-------------|-----------|

| 0x007   | SO / BO     | M         |

| 0x017   | S1 / B1     | M         |

| 0x104   | SO / B1     | M         |

| 0x023   | S2 / B0     | M         |

| 0x203   | SO / BO LRU | M         |

| 0x10F   | SO /B1      | Н         |

Address 007= 0 0 0 0 0 0 0 0 0 1 1 1

This means set  $0 \longrightarrow 0 \mod 16 = 0$ , (miss) we place this block in block 0 of the set 0 in the cache.

OX10F is hit, because this address and OX104 address are found in the same block (same Tag "1").

d. Calculate the miss rate and hit rate.

(5Marks)

Miss rate =

$$5/6$$

3. Consider a system with cache, main memory and disk (or secondary memory) with the following parameters. It takes 10 ns to access cache, 100ns to access RAM and  $10\mu$ s to access disk. The cache miss rate is 3% while miss rate in RAM is 20%. Estimate the average access time. (5Marks)

$$Ta = 0.97 * 10ns + 0.03(0.89 * 100ns + 0.11 * 10 \mu s) =$$

97% of data is found in the cache.

3% of data is found out of the cache: 89% of this 3% data is in RAM, 11% in disk

(Note that access time is the "total time" to get the valid data. For example, RAM access time is the total time to get data from RAM including checking the cache)

4. Consider 8-bit processor that requires 64 Kbytes main memory. Design memory module for the processor using only 8 Kbytes memory chips organized as 16K X 4 bit. Draw your design. (10 Marks)

#### **Solution:**

- Memory locations = 64 K locations, 16 address lines are needed (A0 A15)

- Available chips 8 Kbytes (16K X4), we need 8 chips, each needs 14 (A2 –A15) address lines.

- The memory modules organized as four groups (banks) each contains two chips.

- A0 & A1 used to select one of the four groups. Use 2-to-4 decoder

Question 2 (10 points) What is the 8-bit results after performing each of the following shift operations. Arithmetic Shift Left of (11110010) 111100100 Circular shift left of (11110010) 1110010) Logical shift left of (11110010) 11100100 Arithmetic shift right of (11110010) Logical shift right of (11110010) 111.11 0010 Question 3 (10 points) A computer uses a memory unit with 1K words of 32 bits each. A binary instruction code is stored in one word of memory. The instruction has four parts: an indirect bit, an operation code, a register code part to specify one of 16 registers, and an address part. How many bits are there in the register code part How many bits are there in the address part How many bits are there in the data inputs of the memory How many bits are there in the operation code part How many bits are there in the address inputs of the memory 10 Question 4 (10 points) A digital computer has a common bus system for 32 registers of 64 bits each. The bus is constructed with Lynput multiplexers. How many multiplexers are there in the bus How many selection inputs are there in each multiplexer log 82 = 5 How many 3-state buffers are needed to reconstruct the bus using decoders and 3-state buffers - 4 How many decoders are needed to reconstruct the bus using decoders and 3-state buffers \* 2 7 % What the size of decoder(s) needed to select one destination 5132 32×1 register (for writing bus into a register) 109