# **Birzeit University**

# Faculty of Engineering and Technology Electrical and Computer Engineering Department

# Manual for

# **Digital Electronics and Computer**

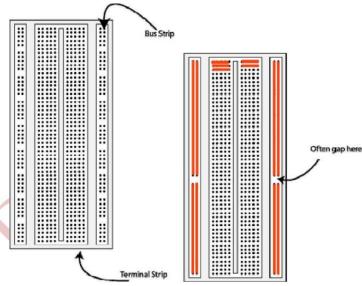

# **Organization Lab**

**ENCS 2110**

# August 2022

# Table of Experiments

| LABORATORY REGULATIONS AND SAFETY RULES                          | III |

|------------------------------------------------------------------|-----|

| EXP. No. 1. Combinational Logic Circuits                         | 1   |

| EXP. No. 2. Comparators, Adders, and Subtractors                 | 21  |

| EXP. No. 3. Encoders, Decoders, Multiplexers, and Demultiplexers |     |

| EXP. No. 4. Digital Circuits Implementation using Breadboard     | 61  |

| EXP. No. 5. Sequential Logic Circuits                            | 73  |

| EXP. No. 6. Sequential Logic Circuits using Breadboard and IC's  |     |

| EXP. No. 7. Constructing Memory Circuits Using Flip-Flops        |     |

| EXP. No. 8. Introduction to QUARTUSII Software                   |     |

| EXP. No. 9. A Simple Security System Using FPGA                  |     |

| EXP. No. 10. Simple Computer Simulation                          |     |

| EXP. No. 11 Arithmetic Elements                                  |     |

# **LABORATORY REGULATIONS AND SAFETY RULES**

The following Regulations and Safety Rules must be observed in the laboratory:

- 1) It is the duty of all concerned who use any electrical laboratory to take all reasonable steps to safeguard the HEALTH and SAFETY of themselves and all other users and visitors.

- Be sure that all equipment is properly working before using them for laboratory exercises. Any defective equipment must be reported immediately to the Lab. Instructors or Lab. Technical Staff.

- 3) Students are allowed to use only the equipment provided in the experiment manual or equipment used for senior project laboratory.

- Power supply terminals connected to any circuit are only energized with the presence of the Instructor or Lab. Staff.

- 5) Students should keep a safe distance from the circuit breakers, electric circuits or any moving parts during the experiment.

- 6) Avoid any part of your body to be connected to the energized circuit and ground.

- 7) Switch off the equipment and disconnect the power supplies from the circuit before leaving the laboratory.

- 8) Observe cleanliness and proper laboratory housekeeping of the equipment and other related accessories.

- 9) Double check your circuit connections before switching "ON" the power supply.

- 10) Make sure that the last connection to be made in your circuit is the power supply and first thing to be disconnected is also the power supply.

- 11) Equipment should not be removed, transferred to any location without permission from the laboratory staff.

- 12) Software installation in any computer laboratory is not allowed without the permission from the Laboratory Staff.

- 13) Computer games are strictly prohibited in the computer laboratory.

- 14) Students are not allowed to use any equipment without proper orientation and actual hands-on equipment operation.

- 15) Smoking and drinking in the laboratory are not permitted

Birzeit University Faculty of Engineering and Technology Electrical and Computer Engineering Department Digital Electronics and Computer Organization Lab ENCS211

# **EXP. No. 1. Combinational Logic Circuits**

# 1.1 Objectives

- To become familiar with AND, OR, NOT, NAND, NOR, XOR operations and their implementation.

- ✤ To construct NOT, AND, OR and XOR gates using NAND gates.

- ✤ To become familiar with concept of Truth table.

- ✤ To implement different Boolean function using NAND gate only.

- ✤ To learn techniques of solution of logic design problems.

- ✤ To become familiar with minimization techniques and with the use of Karnaugh maps.

- ✤ To construct AOI gate with basic gates.

# **1.2 Equipment Required**

- IT-3000 Basic Electricity Circuit Lab

- ✤ IT-3002 Basic Gates.

# 1.3 Pre Lab

\* Review all gates and write the truth table for each of them.

# **1.4 Introduction**

Logic gates are the digital circuits capable of performing a particular logic function by operating on a number of binary inputs. Logic gates can be broadly classified as Basic logic gates, Universal logic gates and other logic gates.

### **1.4.1 Basic logic gates:**

Basic Logic Gates are the fundamental logic gates using which universal logic gates and other logic gates are constructed. These gates are associative and commutative in nature. AND, OR and NOT is the famous examples of basic logic gates.

### 1.4.1.1 AND GATE:

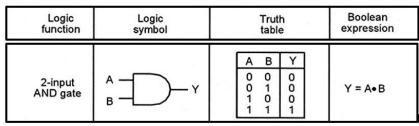

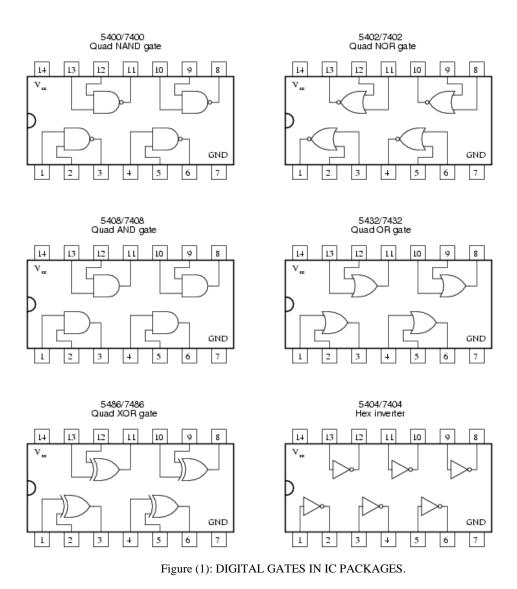

The AND gate performs a logical multiplication commonly known as AND function. The output is high when both the inputs are high. The output is low level when any one of the inputs is low. In Figure (1) shows all information for the AND gate.

Figure (1): The function, symbol, truth table and Boolean expression for AND gate.

### 1.4.1.2 OR GATE:

The OR gate performs a logical addition commonly known as OR function. The output is high when any one of the inputs is high. The output is low level when both the inputs are low. In Figure (2) shows all information for the OR gate.

| Logic              | Logic  | Truth                                                                                                                                                 | Boolean    |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| function           | symbol | table                                                                                                                                                 | expression |

| 2-input<br>OR gate | A<br>B | A         B         Y           0         0         0           0         1         1           1         0         1           1         1         1 | Y = A + B  |

Figure (2): The function, symbol, truth table and Boolean expression for OR gate.

#### 1.4.1.3 NOT GATE:

The NOT gate is called an inverter. The output is high when the input is low. The output is low when the input is high. In Figure (3) shows all information for the NOT gate.

| Logic                  | Logic     | Truth             | Boolean    |

|------------------------|-----------|-------------------|------------|

| function               | symbol    | table             | expression |

| Inverter<br>(NOT gate) | A - V - Y | A Y<br>0 1<br>1 0 | Y = Ā      |

Figure (3): The function, symbol, truth table and Boolean expression for NOT gate.

#### **1.4.2** Universal logic gates

Universal logic gates are the logic gates that are capable of implementing any Boolean function without requiring any other type of gate. We called this gate Universal gates because Universal gates are not associative in nature, but they are commutative in nature. There are two universal logic gates NAND gate and NOR gates.

### **1.4.2.1 NAND GATE:**

The NAND gate is a contraction of AND-NOT. The output is high when both inputs are low and any one of the inputs is low. The output is low level when both inputs are high. In Figure (4) shows all information for the NAND gate.

| Logic                   | Logic  | Truth                                                                                                                                                 | Boolean    |

|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| function                | symbol | table                                                                                                                                                 | expression |

| 2-input<br>NAND<br>gate | A<br>B | A         B         Y           0         0         1           0         1         1           1         0         1           1         1         0 | Y = Ā∙B    |

Figure (4): The function, symbol, truth table and Boolean expression for NAND gate.

### **1.4.2.2 NOR GATE:**

The NOR gate is a contraction of OR-NOT. The output is high when both inputs are low. The output is low when one or both inputs are high. In Figure (5) shows all information for the NOR gate.

| Logic               | Logic       | Truth                                                                                                                                                 | Boolean                |

|---------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| function            | symbol      | table                                                                                                                                                 | expression             |

| 2-input<br>NOR gate | А Доругория | A         B         Y           0         0         1           0         1         0           1         0         0           1         1         0 | $Y = \overline{A + B}$ |

Figure (5): The function, symbol, truth table and Boolean expression for NOR gate.

### 1.4.3 Other logic gates

There are two remaining gates of the primary electronics logic gates: XOR, which stands for Exclusive OR, and XNOR, which stands for Exclusive NOR.

### **1.4.3.1 EX-OR GATE:**

The output is high when any one of the inputs is high. The output is low when both the inputs are low, and both the inputs are high. In Figure (6) shows all information for the EX-OR gate.

| Logic                    | Logic   | Truth                                                                                                                                                 | Boolean    |

|--------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| function                 | symbol  | table                                                                                                                                                 | expression |

| 2-input<br>EX-OR<br>gate | А Д У У | A         B         Y           0         0         0           0         1         1           1         0         1           1         1         0 | Y = A⊕B    |

Figure (6): The function, symbol, truth table and Boolean expression for X-OR gate.

### **1.4.2.2 EX-NOR GATE:**

The X-NOR gate is a contraction of X-OR and NOT. The output is high when number of ones even. The output is low when number of one is odd. In Figure (7) shows all information for the X-NOR gate.

| Logic                     | Logic  | Truth                                                                                                                                                 | Boolean    |

|---------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| function                  | symbol | table                                                                                                                                                 | expression |

| 2-input<br>EX-NOR<br>gate |        | A         B         Y           0         0         1           0         1         0           1         0         0           1         1         1 | Y = A⊕B    |

Figure (7): The function, symbol, truth table and Boolean expression for X-NOR gate.

# 1.5 Procedure

In this experiment we will use NAND and NOR gate to build another gate.

# **1.5.1** The characteristic of NOR gate.

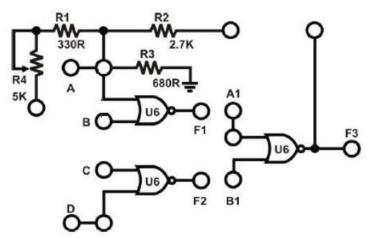

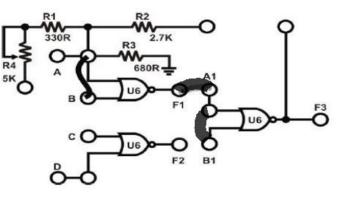

Set module IT-3002 and locate block NOR gate as shown in Figure (8). Connect +5V of module IT-3002 To the +5V output of fixed power supply.

Figure (8): IT-3002 NOR Gate Block.

Then use first gate U6 in Figure (8). Connect A and B in block a with Data switch SW0 and SW1 TTL level in power supply and connect output F1 with Logic Indicator L0. Then write the result in Table (1).

| SW0 | SW1 | <b>F1</b> |

|-----|-----|-----------|

| 0   | 0   |           |

| 0   | 1   |           |

| 1   | 0   |           |

| 1   | 1   |           |

Table 1

3. In this part connect inputs A, B to Data Switches SW0, SW1 and output F1 to Logic Indicator L1. Set SW0 to "0" and SW1 to "0", see the result of the output F1 then change SW1 to "1", and see the output to make it clear go to table 2 and fill the result.

| SW0     | SW1 | <b>F1</b> |

|---------|-----|-----------|

| 0       | 0   |           |

| 0       | 1   |           |

| Table 2 |     |           |

- According to the table does the circuit act as a NOT gate.

- Find another way to build NOT gate using one NOR gate and draw the circuit in box below. (Hint: return to Figure (5) and see the truth table of NOR gate find when the output is opposite of input).

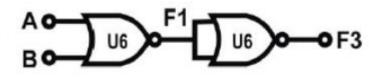

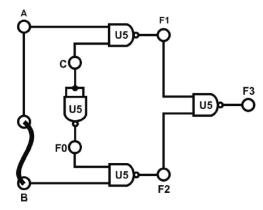

Use two of U6 to construct a buffer shown on Figure (9). Insert connection clips between A and B, connect F1with A1and connect A1 with B1. Connect input A to SW0 and output F3 to L1. fill the table 3.

Figure (9): build buffer using NOR gate

| SW0   | <b>F1</b> |

|-------|-----------|

| 0     |           |

| 1     |           |

| Table | 3         |

- this circuit act as -----.

- 5. We know that OR gate is inverse of NOR gate that mean we can build OR gate using (NOR and NOT) gates and we learn how to build NOT gate using NOR gate only. Draw the following circuit using NOR gate only.

Use two of U6 to construct an OR gate. Insert connection clips between F1-A1 and A1-B1.

Connect inputs A to SW0, B to SW1; and output F3 to L1. Follow the input sequences shown below and record the output states in Table 4.

Figure (10): build OR using NOR gate.

Table 4

| SW0 | SW1 | F3 |

|-----|-----|----|

| 0   | 0   |    |

| 0   | 1   |    |

| 1   | 0   |    |

| 1   | 1   |    |

6. Know we need to build AND gate using NOR gate only to learn how to construct it, let's solve the following equation. We know that AND gate equation is F=A.B if we take inverse for this equation then use De morgan low the equation become F`=......

If we take inverse for above equation, then the equation become:

If we take inverse for above equation, then the equation t

F``=.....

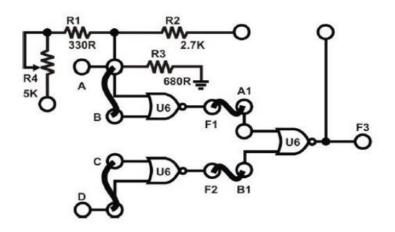

From above equation (F``) we can see that we can build AND gate using one NOR gate and two NOT gate. Insert connection clips according to the Figure (11) below. The circuit will act as an AND gate. Connect A to SW0; D to SW1; F1 to A1; F2 to B1; F3 to L1. Follow the input sequences given below, record the output states in Table 5.

Figure (11): build AND gate using NOR gate using kits.

| SW0 | SW1 | F3 |

|-----|-----|----|

| 0   | 0   |    |

| 0   | 1   |    |

| 1   | 0   |    |

| 1   | 1   |    |

### **1.5.2** The characteristic of NAND gate.

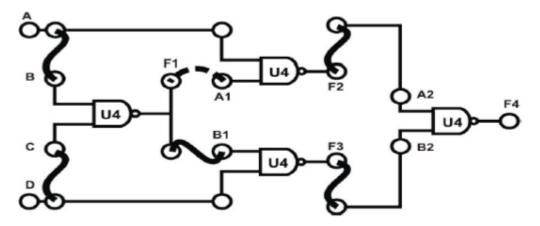

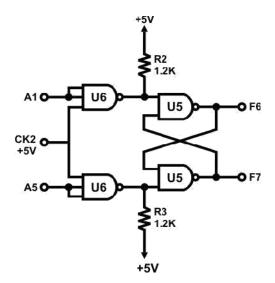

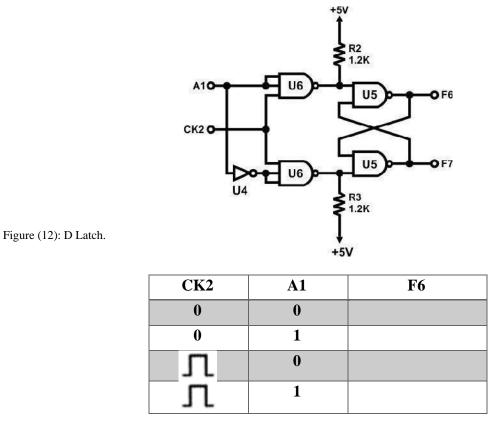

Set module IT-3002 and locate block NAND gate as shown in Figure (12). Connect +5V of module IT-3002 To the +5V output of fixed power supply.

Figure (12): IT-3002 NAND Gate Block.

Then use first gate U4 in Figure (12). Connect A and A1 in block a with Data switch SW0 and SW1 TTL level in power supply and connect output F2 with Logic Indicator L0. Then write the result in Table (6).

| SW0 | SW1     | <b>F1</b> |

|-----|---------|-----------|

| 0   | 0       |           |

| 0   | 1       |           |

| 1   | 0       |           |

| 1   | 1       |           |

|     | Table 6 |           |

3. In this part connect inputs A, A1 to Data Switches SW0, SW1 and output F2 to Logic Indicator L1. Set SW0 to "1" and SW1 to "0", see the result of the output F1 then change SW1 to "1", and see the output to make it clear go to table 7 and fill the result in table.

| SW0 | SW1 | <b>F</b> 1 |

|-----|-----|------------|

| 1   | 0   |            |

| 1   | 1   |            |

- According to the table does the circuit act as a NOT gate?

- Find another way to build NOT gate using one NAND gate and draw the circuit in box below. (Hint: return to Figure (4) and see the truth table of NAND gate find when the output is opposite of input).

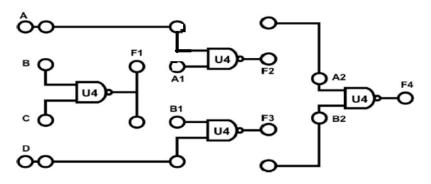

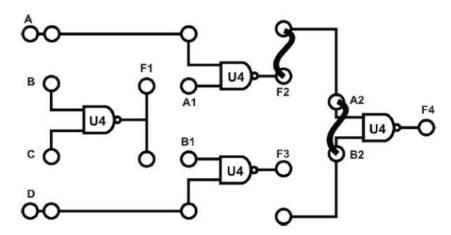

Use two U4 to construct a buffer shown on Figure (13). Insert connection clips between A and A1, connect F2 with A2 and connect A2 with B2. Connect input A to SW0 and output F4 to L1. fill the table 8.

Figure (13): build buffer using NAND gate

| SW0     | <b>F1</b> |

|---------|-----------|

| 0       |           |

| 1       |           |

| Table 8 |           |

- this circuit act as -----.

- 5. We know that AND gate is inverse of NAND gate that mean we can build AND gate using (NAND and NOT) gates and we learn how to build NOT gate using NAND gate only. Draw the following circuit using NAND gate only.

Use two U4 to construct an AND gate. Insert connection clips between F2-A2 and A2-B2. Connect inputs A to SW0, A1 to SW1; and output F4 to L1. Follow the input sequences shown below and record the output states in Table 9.

Figure (14): build AND using NAND gate.

| SW0 | SW1     | F3 |

|-----|---------|----|

| 0   | 0       |    |

| 0   | 1       |    |

| 1   | 0       |    |

| 1   | 1       |    |

| -   | Table 9 | •  |

6. Know we need to build OR gate using NAND gate only to learn how to construct it, let's solve the following equation. We know that OR gate equation is F=A+B if we take inverse for this equation then use De morgan low the equation become

F`=.....

If we take inverse for above equation, then the equation become:

F``=.....

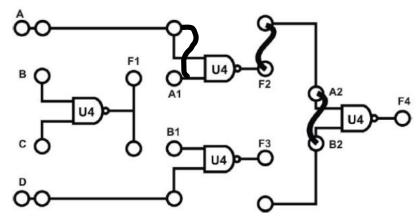

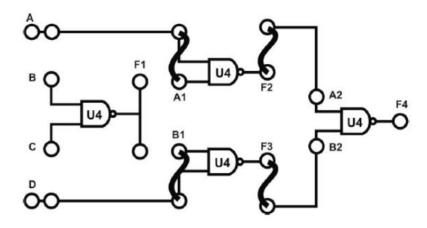

From above equation (F``) we can see that we can build OR gate using one NAND gate and two NOT gate we put it in input as show in Figure (15). The circuit will act as an OR gate. Connect A to SW0; D to SW1; F1 to A1; connect A with A1; and D with B1 and F2 to A2; F3 to B2 then connect the output F4 with L1 .Follow the input sequences given below, record the output states in Table 10.

Figure (15): build OR gate using NAND gate using kits.

| SW0 | SW1 | F3 |

|-----|-----|----|

| 0   | 0   |    |

| 0   | 1   |    |

| 1   | 0   |    |

| 1   | 1   |    |

Table 10

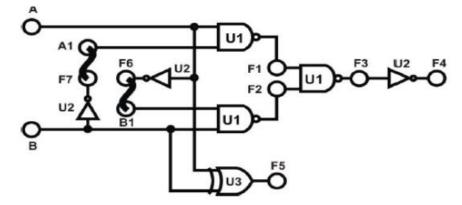

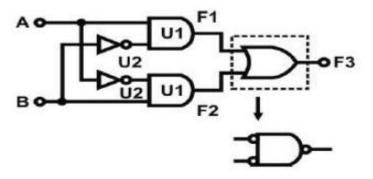

### 1.5.3 XOR Gate Circuit.

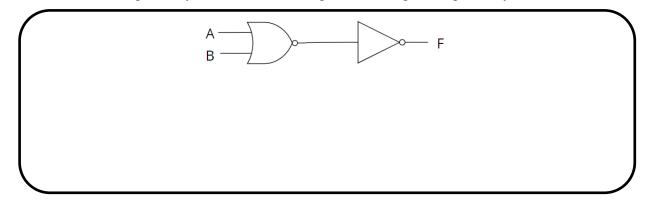

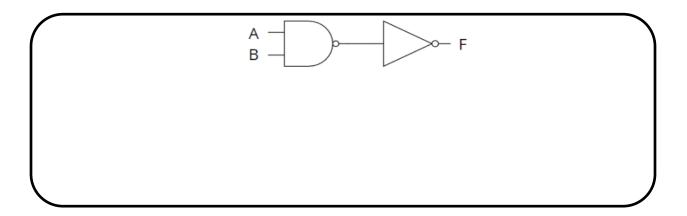

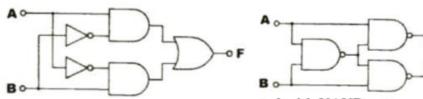

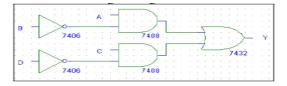

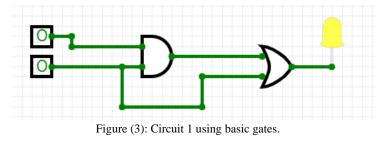

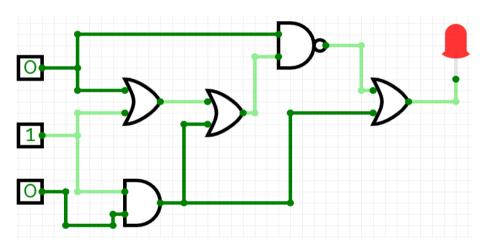

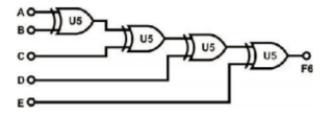

know we went to build XOR gate using NAND gate we know that XOR equation is  $F=AB^+A^B$  we can build it using basic gates as shown in Figure 16-a. or we can build it using NAND gates only as shown in Figure 16-b.

Figure (16-a): Constructed with basic gates.

Figure (16-b): Constructed with NAND gates.

# 1.5.3.1 Constructing XOR gate with NAND gate (Module IT-3002 block NAND gates)

Insert connection clips according to Figure 17. (a) to construct the circuit of Figure 17. Connect inputs A to SW1, D to SW2; outputs F1 to L1, F2 to L2; F3 to L3 and F4 to L4. record the output in Table 11.

Figure (17): Constructed with NAND gates.

| SW1 | SW2 | F1 | F2 | F3 | F4 |

|-----|-----|----|----|----|----|

| 0   | 0   |    |    |    |    |

| 0   | 1   |    |    |    |    |

| 1   | 0   |    |    |    |    |

| 1   | 1   |    |    |    |    |

Table 11

-Now determine the Boolean expression for F1, F2, F3 and F4.

F1=..... F2=..... F3=..... F4=....

### 1.5.3.2 Constructing XOR gate with Basic Gate (Module IT-3002 block Comparator1)

Insert connection clips according to Figure 18-a.

• to construct the equivalent circuit of Figure 18-b.

Figure (18-a): Constructed with basic gates using kits.

Figure (18-b): equivalent circuit.

Connect inputs A, B to SW1, SW2; outputs F1, F2, F3 to L1, L2, L3 as shown in Figure 18-a. write the result in Table 12.

| SW1      | SW2 | <b>F1</b> | <b>F2</b> | <b>F3</b> |

|----------|-----|-----------|-----------|-----------|

| 0        | 0   |           |           |           |

| 0        | 1   |           |           |           |

| 1        | 0   |           |           |           |

| 1        | 1   |           |           |           |

| Table 12 |     |           |           |           |

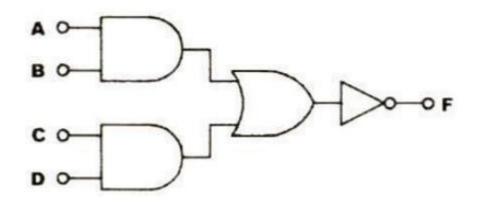

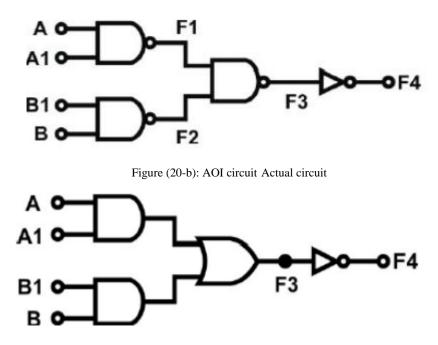

### 1.5.4 AOI Gate Circuits.

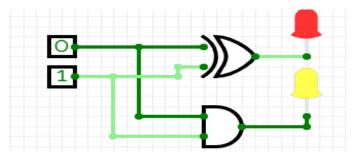

AND-OR-INVERTER (AOI) gates consist of two AND gates, one OR gate and one INVERTER (NOT) gate. The symbol of an AOI gate is shown in Fig. 1.15. The Boolean expression for the output F is F = (AB+CD)' ...... (1)

Figure (19): AOI gate.

By De Morgan's theorem, Eq. (1) can be converted to:

$F = (A'+B') (C'+D') \dots (2)$

Eq. (1) is also referred to as "Sum of Products".

Eq. (2) is also referred to as "Product of Sums".

Basically, the A-Q-I gate is a "Sum of Products" logic combination

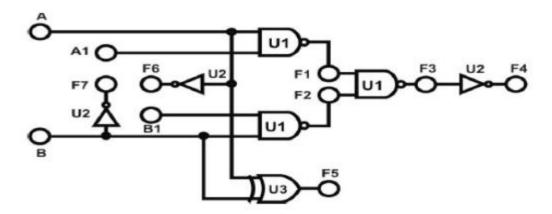

Use U1 and U2 on block Comparator 1 of module IT-3002, shown in Fig. 1.20 (a), to construct the A-O-I gate of Fig. 1.20 (b). Fig. 1.20 (c) is the equivalent A-O-I circuit.

Figure (20-a): AOI circuit Wiring diagram

Figure (20-c): AOI circuit Equivalent circuit

- Connect inputs A, A1, B, B1 to Date Switches SW0, SW1, SW2 and SW3 respectively.

Connect outputs F3, F4 to Logic Indicators L1 and L2.

- Set B×B1to "0", follow the input sequences for A, A1 in Table 13 and record the outputs

| Α | A1 | F3 | F4 |

|---|----|----|----|

| 0 | 0  |    |    |

| 0 | 1  |    |    |

| 1 | 0  |    |    |

| 1 | 1  |    |    |

Table 12

- Does F3 act as an AND gate between A and A1?

- When  $B \times B1$  is "0", does F3 act as an AND gate between A and A1? (F3=A×A1).

- WhenA1×A is "0", follow the input sequences for B, B1 in Table 14 and record the Outputs.

| В | B1 | F3       | F4 |

|---|----|----------|----|

| 0 | 0  |          |    |

| 0 | 1  |          |    |

| 1 | 0  |          |    |

| 1 | 1  |          |    |

| - | •  | Table 13 | ·  |

- Does F3 act as an AND gate between B and B1?

- WhenA×A1 is "0", does F3 act as an AND gate between B and B1? Does F3 equal toA×A1+B×B1?

# 1.6 Post Lab

- Draw the logic diagram showing the implementation of the following Boolean equation using "NAND" gates

- a) F = AB (CA).

- b) F = (D.A) + (C.B)

- c) F = XZ + Y'Z + X'YZ

- Draw the logic diagram of the following Boolean equations using NOR gates.

a)

$$F=(A+B)(CD+A)$$

- b) F= (ABC+D) C

- c) F = (X+Z) (Y'+Z) (X'+Y+Z)

- Implement the OR operation using AND, NOT gate. Draw the logic diagram and write Boolean equation.

- Implement the AND gate using OR, NOT gate. Draw the logic diagram and write Boolean equation.

- Prove that the equality operation Fl =AB+A'B' is the inverse of exclusive OR operation

F2=AB'+A'B (use Demerger's theorem).

- Show how is it possible to reduce Boolean expressions by means of Karnaugh map

a) F1 = A'B'C + ABC' + A'BC' + AB'C

b) F2=A'D+A'C+BD+AB'D'

c) F3 = A'BCD + ABCD' + A'BCD' + ABCD'

d) F4= A'B'C'D' + AB'CD' + A'B'CD' + A'BC'D'

Birzeit University Faculty of Engineering and Technology Electrical and Computer Engineering Department Digital Electronics and Computer Organization Lab ENCS211

# EXP. No. 2. Comparators, Adders, and Subtractors

# 2.1 Objectives

- To understand the construction and operating principle of digital comparators

- To construct comparators with basic gates and ICs

- To implement half- and full adders using basic logic gates and ICs

- To implement a 4-bit adder unit(s)/ICs to add 4-bit numbers

- To understand the theory of complements

- ✤ To construct half- and full- subtractor circuits

# 2.2 Equipment Required

- IT-3000 Basic Electricity Circuit Lab

- IT-3002 Basic Gates Circuit

- IT-3003 Adder/Subtractor Circuits

# 2.3 Pre Lab

- 1) Prepare all sections and work out all the required designs.

- 2) Build half adder using basic gates.

- 3) Build the above circuit using universal gates.

- 4) Build a full adder using basic gates.

- 5) Build a full adder using half adder and another gate.

- 6) Build a 4-bit adder using a full adder.

- 7) Build a 4-bit subtractor using basic gates.

Page | 21

# 2.4 Theory

### 2.4.1 Half- and Full- Adder Circuits:

### 2.4.1.1 Half Adder:

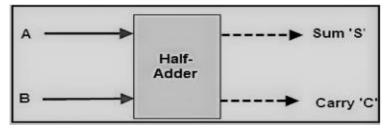

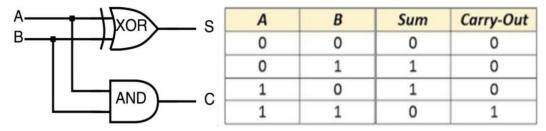

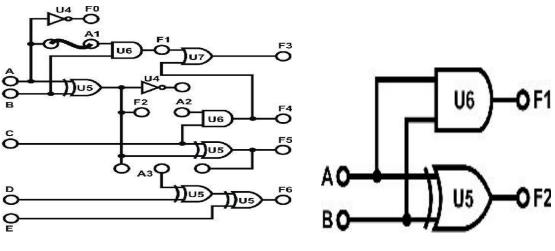

The half adder accepts two binary digits on its inputs and produces two binary digits outputs, a sum bit, and a carry bit. The half adder is an example of a simple, functional digital circuit built from two logic gates. The half adder adds to one-bit binary numbers (AB). The output is the sum of the two bits (S) and the carry (C)as shown in Figure 1.

Figure (1): Half-Adder Functional Diagram.

Note how the same two inputs are directed to two different gates. The inputs to the XOR gate are also the inputs to the AND gate. The input "wires" to the XOR gate are tied to the input wires of the AND gate; thus, when voltage is applied to the A input of the XOR gate, the A input to the AND gate receives the same voltage. As shown in Figure 2.

Figure (2): Half-Adder circuit and truth table.

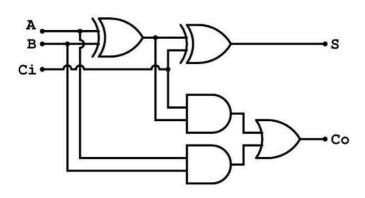

#### 2.4.1.2 Full Adder:

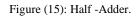

The full adder accepts two inputs bits and an input carry and generates a sum output and an output carry. The full-adder circuit adds three one-bit binary numbers (Cin, A, B) and outputs two one-bit binary numbers, a sum (S) and a carry (Cout) as shown in Figure 3. The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. binary numbers.

Figure (3): Full-Adder Functional Diagram.

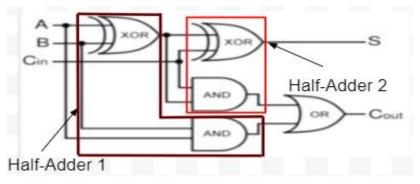

In Figure 4-a, if you look closely, you'll see the full adder is simply two half adders joined by an OR. We can implement a full adder circuit with the help of two half adder circuits. The first half adder will be used to add A and B to produce a partial Sum. The second half adder logic can be used to add CIN to the Sum produced by the first half adder to get the final S output. If any of the half-adder logic produces a carry, there will be an output carry. Thus, COUT will be an OR function of the half-adder Carry outputs. We can see the truth table for full adder in Figure 4-b.

Figure(4-a): Full-Adder Circuit.

| Α | В | Carry-In | Sum | Carry-Out |

|---|---|----------|-----|-----------|

| 0 | 0 | 0        | 0   | 0         |

| 0 | 0 | 1        | 1   | 0         |

| 0 | 1 | 0        | 1   | 0         |

| 0 | 1 | 1        | 0   | 1         |

| 1 | 0 | 0        | 1   | 0         |

| 1 | 0 | 1        | 0   | 1         |

| 1 | 1 | 0        | 0   | 1         |

| 1 | 1 | 1        | 1   | 1         |

Figure(4-b): Full-Adder Truth table.

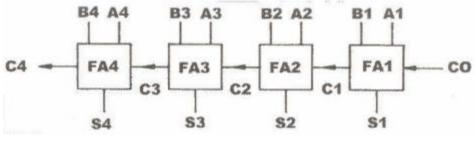

To perform additions of numbers greater than 2-bits in length, the connection shown in Figure 5, or "Parallel Input" should be used to generate sums simultaneously. However, the sum of the next adder will be stable only after the previous adder's carry has stabilized. For example, in Figure 5, the sum of FA2 will not be stable unless the carry of FA 1 is stable.

Figure (5): 4-bit adder.

When FA1 adds A1 and B1, a sum S1 and a carry C1 is generated. C1 will be added to A2 and B2 by FA2, generating another sum S2 and another carry C2. In the case of Figure 5, the sum of the four adders do not stabilize at the same time, delaying the adding process. This delay can be eliminated by using the "Look-Ahead" adder.

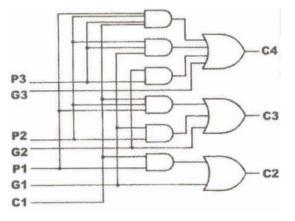

**Look-ahead adders** do not have to wait for the previous adder to stabilize before performing the next addition, saving valuable time. In Boolean expression we assume:

Pi =Ai  $\oplus$ Bi Gi =Ai x Bi The output and carry can be expressed as: Si = Pi  $\oplus$  Cj Ci+1 = Gi + PiCi Page | 24 Gi is called "Carry Generate". When Ai and Bi are both "1", Gi is "1" and unrelated to the carry input. Pi is called "Carry Transmit", related to the carry transmit between Ci and Ci+1. If we substitute the carry function of each stage by the previous carry, we get:

$$C2 = G1 + P1 C1$$

$C3 = G2 + P2 C2 = G2 + P2 G1 + P2 P1 C1$

$C4=G3+P3C3=G3+P3P2G1+P3P2P1C1$

Figure 6 shows the carry path of a look-ahead adder. The 74182 is a look-ahead adder TTL-IC.

Figure (6): look-ahead adder.

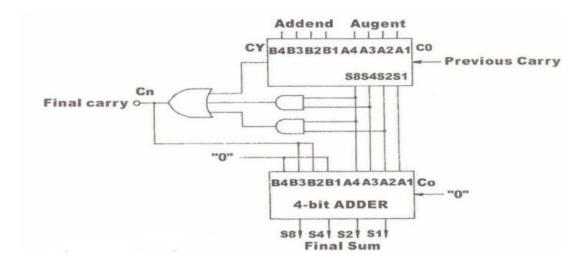

**Binary adders can be converted into BCD adders**. Since BCD has 4 bits with the largest number being 9; and the largest 4-bit binary number is equivalent to 15, there is a difference of 6 between the binary and the BCD adder: Under following conditions 6 must be added when binary adders are used to add BCD codes:

- 1. When there is any carry.

- 2. When the sum is larger than 9.

If the order of priority is S8, S4, S2, S1 and the sum is larger than 9 then S8 x S4 + S8u x S2. If any carry is involved, assuming the carry is CY, under this term, 6 must be added:

CY + S8 X S4 + S8 X S2.

Figure (7): BCD adder.

### 2.4.2 Half- and Full-Subtractor Circuits:

### 2.4.2.1 Half Subtractor:

Binary subtraction is usually performed by using 2's complement. Two steps are required to obtain 2's complement. First, the subtrahend is inverted to 1's complement, i.e., a "1" to a "0" and a "0" to a "1". Secondly, a "1" is added to the least significant bit of the subtrahend in 1's complement.

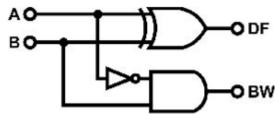

A half-subtractor performs the task if subtraction 1-bit at a time regardless of whether the minuend is greater or less than the subtrahend. "Borrow" from previous subtraction is not taken into consideration

| Minuend | Subtrahend | Difference | Borrow |

|---------|------------|------------|--------|

| Α       | В          | DF         | BW     |

| 0       | 0          | 0          | 0      |

| 0       | 1          | 1          | 1      |

| 1       | 0          | 1          | 0      |

| 1       | 1          | 0          | 0      |

(a) Truth table.

Figure (8): Half-Subtractor.

#### 2.4.2.2 Full Subtractor:

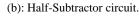

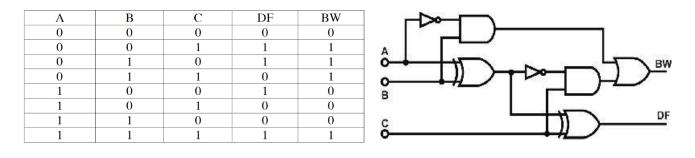

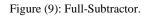

full subtractor is a combinational circuit that performs subtraction of two bits, one is minuend and other is subtrahend, taking into account borrow of the previous adjacent lower minuend bit. This circuit has three inputs and two outputs. The three inputs A, B and Bin, denote the minuend, subtrahend, and previous borrow, respectively. The two outputs, D and Bout represent the difference and output borrow, respectively. Although subtraction is usually achieved by adding the complement of subtrahend to the minuend, it is of academic interest to work out the Truth Table and logic realization of a full subtractor; x is the minuend; y is the subtrahend; z is the input borrow; D is the difference; and B denotes the output borrow. The corresponding maps for logic functions for outputs of the full subtractor namely difference and borrow.

(a) Truth table.

(b): Full-Subtractor circuit.

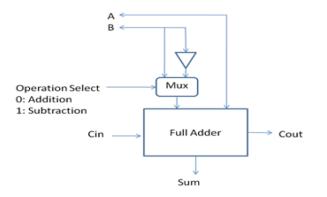

From a 4-bit adder circuit, we can assemble subtractor circuits of 4-bit or longer. Figure 10 shows a dual-purpose adder/ subtractor circuit. When Bn-1= "0" additions are performed and all XOR gates act as buffers. When Bn - 1 = "1" subtractions will be performed and all XOR gates act as NOT gates. Y inputs use 1's complemented and adds a "1" from Cin. The outputs are Cn (carry) and Bn (borrow), Cn and Bn are dependent on Bn-1.

Figure (10): Dual-purpose adder/subtractor circuit.

### 2.4.3 Comparator Circuit

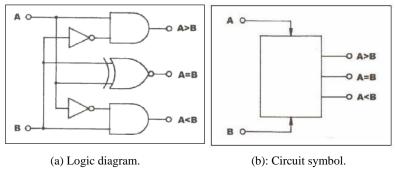

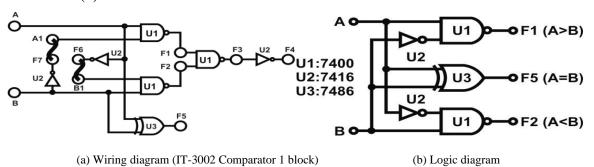

At least two numbers are required to perform any comparison. The simplest form of the comparator has two inputs. If the two inputs are called A and B, then there are three possible outputs: A>B, A=B, and A<B. Figure 11 shows the schematic and symbol diagrams of a simple 1-bit comparator circuit.

Figure (11): Comparator circuit.

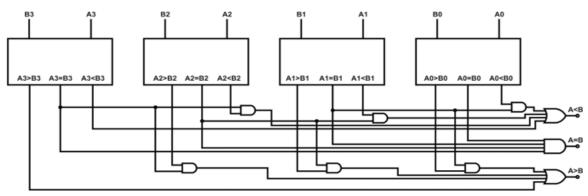

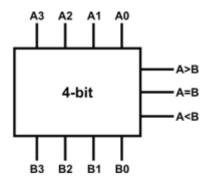

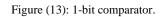

In actual applications, 4-bit comparators are used most often. In a 4-bit comparator, each bit represents  $2^0$ ,  $2^1$ ,  $2^2$ , and  $2^3$ . Comparison will start from the most significant bit ( $2^3$ ), if input A is greater than input B at the  $2^3$  bits, the "A>B" output will be in the high state. If A and B are equal at the  $2^3$  bits, the comparison will be carried out at the next highest bit ( $2^2$ ). If there is still no result at this bit, the process is repeated again at the next bit. At the lowest bit ( $2^0$ ), if the inputs are still equal then the "A=B" output will be in the high state. Figure 12 shows the schematic and symbol of a 4-bit comparator.

(a): A 4-bit comparator constructed with four 1-bit comparators.

Figure (12): Expansion of 1-bit comparators to construct 4-bit comparator.

# 2.5 Procedure

### 2.5.1 Comparator Circuits

### 2.5.1.1 Constructing Comparator with Basic Logic Gates

Set module IT-3002 block Comparator 1.Insert connection clips according to Figure 13 (a). U1, U2, and U3 will be used to construct the 1-bit comparator shown in Fig. 13 (b).

The inputs are triggered by high state voltage. Connect inputs A and B to Data Switches SW1 and SW2. The outputs are triggered by low state voltage. Connect outputs F1, F2, F5 to Logic Indicators L1, L2, and L3 respectively. Then Follow the input sequences the result in Table (1).

| INPUTS |     |                                              | OUTPUTS   |    |    |

|--------|-----|----------------------------------------------|-----------|----|----|

| SW2    | SW1 |                                              | <b>F1</b> | F2 | F5 |

| 0      | 0   | A=B                                          |           |    |    |

| 0      | 1   | A>B                                          |           |    |    |

| 1      | 0   | A <b< td=""><td></td><td></td><td></td></b<> |           |    |    |

| 1      | 1   | A=B                                          |           |    |    |

Table 1

### 2.5.1.2 Constructing Comparator with TTL IC

Block (Comparator 2) of module IT-3002 will be used in this section. U5 is a 74LS85 4-bit Comparator IC shown in Figure 14.

Figure (14): 4-bit Comparator IC (IT-3002 block Comparator 2).

- Connect input in left side of the blook A<B to SW1, A=B to SW2, A>B to SW3. The inputs A0~A3 and B0~B3 of the 74LS85 are also connected to the BCD rotary switch and connect output in right side of the blook A<B, A=B and A>B to Leds.

- 3. Set comparing inputs A0~A3=As, B0~B3=Bs, and As=Bs from the rotary switch, follow cascading inputs sequences in Table 2 and record the outputs.

| INPUTS |     |                                                                       | OUTPUTS |     |                   |

|--------|-----|-----------------------------------------------------------------------|---------|-----|-------------------|

| A>B    | A=B | A <b< td=""><td>A&gt;B</td><td>A=B</td><td>A<b< td=""></b<></td></b<> | A>B     | A=B | A <b< td=""></b<> |

| 0      | 0   | 1                                                                     |         |     |                   |

| 0      | 1   | 0                                                                     |         |     |                   |

| 0      | 1   | 1                                                                     |         |     |                   |

| 1      | 0   | 0                                                                     |         |     |                   |

| 1      | 0   | 1                                                                     |         |     |                   |

| 1      | 1   | 1                                                                     |         |     |                   |

| L      | I   | I                                                                     | Table 2 |     | 1                 |

Compare the results with the function table of **74LS85** (page 2 of the datasheet)<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> <u>https://www.futurlec.com/74LS/74LS85.shtml</u> Page | 31

- 4. Set SW3 to "0"; SW2 to "1"; SW1 to "0". Observe and record the outputs under the following conditions:

- a) As >Bs

- b) As=Bs

- c) As<Bs

### <u>Design a three-bit comparator (using the basic comparator) and hand it out to your</u> <u>TA. (Pre Lab).</u>

### 2.5.2 Half- and Full-Adder Circuits

### 2.5.2.1 Half Adder

### <u>Hand out, Design, Boolean function, and truth table of half- and full-adder to your TA.</u> (Pre Lab).

Set module IT-3003 and locate block Half-Adder. Insert connection clips according to Figure 15 (a), using U5 and U6 to assemble the half-adder circuit of Figure 15 (b). Connect +5V of module IT-3003 to the +5V output of the fixed power supply.

(a) Wiring diagram (IT-3003 Half-Adder block)

(b) Half-Adder circuit

2. Connect inputs A, B to Date Switches SW0, SW1 and connect outputs F1, F2 to logic indicators L1 and L2. Follow the input sequences for A and B in Table 3 and record the output states.

| INP     | UTS     | OUTPUTS    |          |  |

|---------|---------|------------|----------|--|

| SW1 (B) | SW0 (A) | F1 (CARRY) | F2 (SUM) |  |

| 0       | 0       |            |          |  |

| 0       | 1       |            |          |  |

| 1       | 0       |            |          |  |

| 1       | 1       |            |          |  |

|         |         | Table 3    |          |  |

- 3. Reassemble the circuit according to Figure 16 (a) to construct the full-adder circuit shown in Figure 16 (b).

- 4. Connect A, B, C to SW1. SW2 and SW3. A and B are augends while C is the previous carry. Connect F3 to L1, F5 to L2. Follow the input sequences in Table 4 and record output states

(a) Wiring diagram (IT-3003 Full-Adder block)

(b) Full-Adder circuit

Figure (16): Full adder

| INPUTS  |                                       | OUTP                                                                                                                                                                                                                                          | UTS                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW2 (B) | SW1 (A)                               | F3 (CARRY)                                                                                                                                                                                                                                    | F5 (SUM)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0       | 0                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0       | 1                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1       | 0                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1       | 1                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0       | 0                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0       | 1                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1       | 0                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1       | 1                                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | SW2 (B)<br>0<br>1<br>1<br>0<br>0<br>1 | SW2 (B)       SW1 (A)         0       0         0       1         1       0         1       1         0       0         1       1         0       0         1       1         0       0         1       0         1       0         1       0 | SW2 (B)         SW1 (A)         F3 (CARRY)           0         0         0           0         1         1           1         0         1           1         0         1           0         0         1           1         0         1           0         0         1           1         1         1           0         0         1           1         1         1           1         0         1           1         0         1 |

Table 4

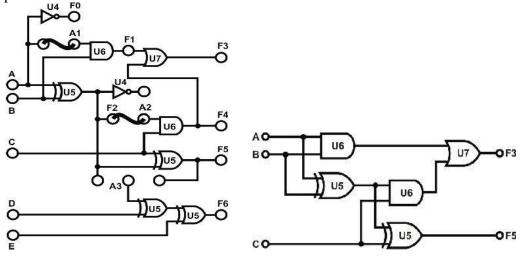

#### 2.5.2.2 Constructing 4-Bit Full-Adder with IC

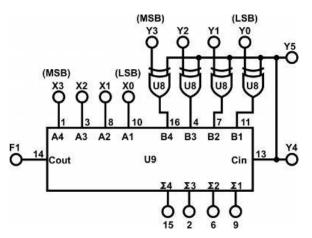

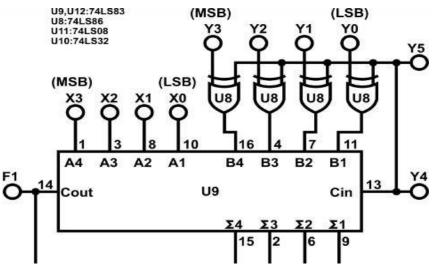

1. U9 on block Full-Adder of module IT-3003 is used as a 4-bit adder. Connect input Y5 to SW0, so the XOR gates U8, which are connected to Y0~Y3, will act as buffers.

Connect input X0~X3 (addends), Y0~Y3 (augends) to DIP switches DIP2.0~2.3 and DIP1.0~1.3 respectively as shown in Figure 17. Connect F1,  $\Sigma 1$ ,  $\Sigma 2$ ,  $\Sigma 3$ ,  $\Sigma 4$  to L1~L5. Follow input sequences in Table 5 and set SW0 to "0"; record F1 and  $\Sigma$  in binary numbers.

X = X3X2X1X0

Y = Y3Y2Y1Y0

$\Sigma = \Sigma 3 \Sigma 2 \Sigma 1 \Sigma 0$

Figure (17): Wiring Diagram (IT-3003 4-bit Full-Adder block).

|           |    |    | INP | UTS |    |    |    |    |    | OU | TPUTS | 5         |

|-----------|----|----|-----|-----|----|----|----|----|----|----|-------|-----------|

| <b>Y3</b> | Y2 | Y1 | Y0  | X3  | X2 | X1 | XO | Σ4 | Σ3 | Σ2 | Σ1    | F1(CARRY) |

| 0         | 0  | 0  | 0   | 0   | 0  | 0  | 0  |    |    |    |       |           |

| 0         | 0  | 0  | 0   | 0   | 0  | 0  | 1  |    |    |    |       |           |

| 0         | 0  | 0  | 0   | 0   | 1  | 1  | 0  |    |    |    |       |           |

| 0         | 0  | 0  | 0   | 1   | 0  | 0  | 1  |    |    |    |       |           |

| 0         | 0  | 0  | 0   | 1   | 1  | 1  | 1  |    |    |    |       |           |

| 0         | 0  | 0  | 1   | 0   | 0  | 1  | 1  |    |    |    |       |           |

| 0         | 0  | 0  | 1   | 0   | 1  | 1  | 0  |    |    |    |       |           |

| 0         | 0  | 0  | 1   | 1   | 0  | 0  | 0  |    |    |    |       |           |

| 0         | 0  | 1  | 1   | 0   | 1  | 1  | 0  |    |    |    |       |           |

| 0         | 1  | 0  | 0   | 1   | 0  | 0  | 0  |    |    |    |       |           |

| 0         | 1  | 0  | 0   | 1   | 1  | 1  | 1  |    |    |    |       |           |

| 1         | 0  | 0  | 0   | 0   | 1  | 1  | 1  |    |    |    |       |           |

| 1         | 0  | 0  | 1   | 1   | 0  | 0  | 1  |    |    |    |       |           |

| 1         | 0  | 1  | 0   | 1   | 0  | 1  | 1  |    |    |    |       |           |

Table 5

# 2.5.2.3 High-Speed Adder Carry Generator Circuit

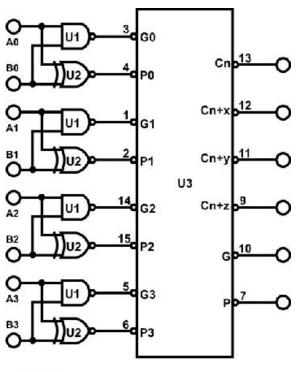

1. U3 (74182) on block High-Speed Adder of module IT-3003 is used to construct a carry generator circuit shown in Figure 18.

U1: 74LS00 U2: 74LS266 U3: 74LS182

Figure (18): Carry generator circuit.

Connect inputs A0~A3 (addends) to DIP Switches 1.0~1.3; B0~B3 (augends) to DIP2.0~2.3, connect Cn to SW0, and set SW0 to "0". Follow the input sequences in Table 6 and record output states.

|    | INPUTS |           |    |    |    |    |    |      | (    | DUTPUTS | 1 | 1      |

|----|--------|-----------|----|----|----|----|----|------|------|---------|---|--------|

| B3 | B2     | <b>B1</b> | BO | A3 | A2 | A1 | A0 | Cn+x | Cn+y | Cn+z    | G | –<br>P |

| 0  | 0      | 0         | 1  | 0  | 0  | 0  | 1  |      |      |         |   |        |

| 0  | 0      | 1         | 0  | 0  | 0  | 1  | 0  |      |      |         |   |        |

| 0  | 0      | 0         | 0  | 0  | 0  | 1  | 0  |      |      |         |   |        |

| 0  | 0      | 1         | 1  | 0  | 0  | 1  | 1  |      |      |         |   |        |

| 1  | 0      | 1         | 0  | 1  | 0  | 0  | 0  |      |      |         |   |        |

| 1  | 1      | 1         | 0  | 1  | 1  | 1  | 1  |      |      |         |   |        |

| 1  | 1      | 1         | 1  | 1  | 1  | 0  | 1  |      |      |         |   |        |

| 0  | 1      | 1         | 1  | 0  | 1  | 1  | 0  |      |      |         |   |        |

| 1  | 0      | 0         | 1  | 0  | 1  | 0  | 1  |      |      |         |   |        |

|    |        |           |    |    |    |    |    |      |      |         |   |        |

|    |        |           |    |    |    |    |    |      |      |         |   |        |

|    |        |           |    |    |    |    |    |      |      |         |   |        |

|    |        |           |    |    |    |    |    |      |      |         |   |        |

|    |        |           |    |    |    |    |    |      |      |         |   |        |

|    |        |           |    |    |    |    |    |      |      |         |   |        |

Table 6

- Compare the results with the truth table of 74LS182 (datasheet).

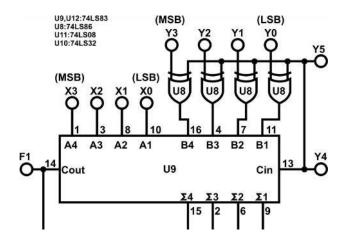

#### 2.5.2.4 2.5.2.4 Constructing BCD Adder

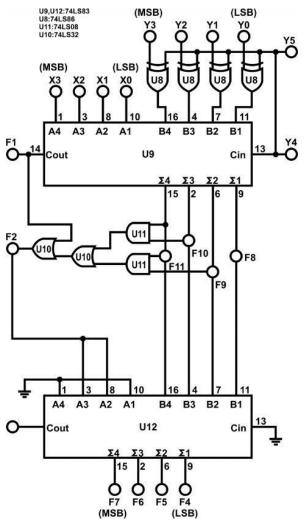

1. The circuit shown in Figure 19 will act as a BCD adder.

Figure (19): Wiring Diagram (IT-3003 BCD Adder).

Connect inputs X0~X3 to DIP 1.0~1.3; Y0~Y3 to DIP 2.0~2.3; Y5 to "0". U9 and U12 are 74LS83 look-ahead 4-bit BCD adders, connect outputs F8~F11 to the inputs of the 7-Segment display SEG-1. Connect F1, F2 to Logic Indicators L4 and L5.

Connect outputs F4~F7 of U12 to another 7-Segment display SEG-3 and F3 to L10.

3. F8~F11 are the sum of X0~X3 added to Y0~Y3 while F1 is the carry. Follow the input sequences for X0~X3 and Y0~Y3 in Table 7 and record the output states.

|    |    |           | INPU | JTS |    |    |    |           | OUTE | PUTS ( | U9)       |           |           | LA        | ST (I     | J <b>12</b> ) |           |           |

|----|----|-----------|------|-----|----|----|----|-----------|------|--------|-----------|-----------|-----------|-----------|-----------|---------------|-----------|-----------|

| X3 | X2 | <b>X1</b> | XO   | Y3  | Y2 | Y1 | Y0 | <b>F1</b> | F11  | F10    | <b>F9</b> | <b>F8</b> | <b>F2</b> | <b>F3</b> | <b>F7</b> | <b>F6</b>     | <b>F5</b> | <b>F4</b> |

| 0  | 0  | 0         | 0    | 0   | 0  | 0  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 0  | 0         | 1    | 0   | 0  | 1  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 0  | 1         | 1    | 0   | 1  | 0  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 0  | 1         | 0    | 0   | 0  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 0  | 1         | 0    | 1   | 0  | 0  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 0  | 1         | 1    | 0   | 1  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 0         | 0    | 0   | 0  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 0         | 0    | 0   | 1  | 0  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 0         | 0    | 0   | 1  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 0         | 1    | 0   | 1  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 1         | 0    | 0   | 1  | 1  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 1         | 1    | 1   | 0  | 0  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 0  | 1  | 1         | 1    | 1   | 0  | 0  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 0  | 0         | 0    | 1   | 0  | 0  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 0  | 0         | 1    | 1   | 0  | 0  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 0  | 1         | 0    | 1   | 0  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 0  | 1         | 0    | 1   | 0  | 1  | 1  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 0  | 1         | 0    | 1   | 1  | 0  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 0  | 1         | 1    | 1   | 1  | 1  | 0  |           |      |        |           |           |           |           |           |               |           |           |

| 1  | 1  | 1         | 1    | 1   | 1  | 1  | 1  |           |      |        |           |           |           |           |           |               |           |           |

|    | •  |           |      |     |    |    |    | Table 7   |      |        | •         | •         |           |           |           |               |           |           |

#### 2.5.3 Half- and Full Subtractor Circuits 2.5.3.1 Constructing Half-/Full Subtractors with basic logic Gates.

# Hand out, Design, Boolean function, and truth table of half- and full-adder to your TA. (Pre Lab).

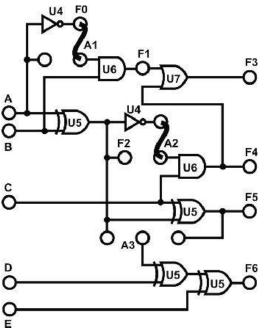

- 1. Set module IT-3003 and locate block Half-Adder. Insert connection clips according to Figure 20.

- 2. Connect inputs A~C to Data Switches SW0~SW2; Outputs F2 to Logic Indicator L1; F1 to L2; F3 to L3; and F5 to L4. When C=0 the circuit is a half-subtractor. F1 is the borrow output; F2 is the difference and F5=F2; F4=0; F3=F1. When C=1 the circuit is a full-subtractor. F3 is the borrow output and F5 is the difference output.

Figure (20): Wiring diagram (Half-subtractor).

|                          | INPUTS |   |   |            | OUT | PUTS      |    |

|--------------------------|--------|---|---|------------|-----|-----------|----|

|                          | С      | Α | B | <b>F</b> 1 | F2  | <b>F3</b> | F. |

| Half-                    | 0      | 0 | 1 |            |     |           |    |

| subtractor<br>Half-adder | 0      | 0 | 0 |            |     |           |    |

|                          | 0      | 1 | 1 |            |     |           |    |

|                          | 0      | 1 | 0 |            |     |           |    |

| Full-                    | 1      | 0 | 0 |            |     |           |    |

| subtractor               | 1      | 0 | 1 |            |     |           |    |

| Full-adder               | 1      | 1 | 0 |            |     |           |    |

|                          | 1      | 1 | 1 |            |     |           |    |

#### 2.5.3.2 Constructing 4-Bit Full-Subtractor with IC

1. Use Module IT-3003 block Full Adder (Figure 21). Connect inputs X3~X0 (minuend) to DIP Switch 1.3~1.0; Y3~Y0 (subtrahend) to DIP 2.3~2.0; Y5 to SW0.

Connect outputs F1 to L4; F11~F8 to L3~L0. To execute the subtract operation,

set SW0 to "1" (or Cin of U9=1). Follow the input sequences below and record the output states in Table 9.

Figure (21): Wiring Diagram for full subtractor (IT-3003 4-bit Full-Adder block)

|    | INPUTS |           |    |    |    |    |    |           |     | UTPU | ГS        |           |

|----|--------|-----------|----|----|----|----|----|-----------|-----|------|-----------|-----------|

| X3 | X2     | <b>X1</b> | X0 | Y3 | Y2 | Y1 | Y0 | <b>F1</b> | F11 | F10  | <b>F9</b> | <b>F8</b> |

| 0  | 1      | 0         | 0  | 0  | 1  | 0  | 0  |           |     |      |           |           |

| 0  | 1      | 0         | 0  | 0  | 0  | 1  | 1  |           |     |      |           |           |

| 1  | 0      | 0         | 0  | 0  | 0  | 1  | 1  |           |     |      |           |           |

| 1  | 0      | 0         | 0  | 0  | 0  | 0  | 1  |           |     |      |           |           |

| 1  | 0      | 0         | 1  | 1  | 0  | 0  | 0  |           |     |      |           |           |

| 1  | 0      | 0         | 1  | 0  | 1  | 1  | 1  |           |     |      |           |           |

| 1  | 0      | 1         | 0  | 0  | 1  | 1  | 0  |           |     |      |           |           |

| 1  | 0      | 1         | 0  | 0  | 1  | 0  | 1  |           |     |      |           |           |

| 1  | 0      | 1         | 1  | 1  | 0  | 1  | 0  |           |     |      |           |           |

| 1  | 1      | 1         | 1  | 1  | 0  | 1  | 0  |           |     |      |           |           |

Table 9

# 2.5 Post Lab

- 1. Design 8-bit BCD adder-subtractor.

- 2. Design 8-bit comparator using 2 of 4-bit comparator.

- 3.A 4-inputs, 3-outputs circuit that compares 2-bit unsigned numbers and outputs a '1' on one of three output lines according to whether the first number is greater than, equal to, or less than the other number. You can only use two  $4 \times 1$  multiplexers.

Birzeit University Faculty of Engineering and Technology Electrical and Computer Engineering Department Digital Electronics and Computer Organization Lab ENCS211

# EXP. No. 3. Encoders, Decoders, Multiplexers, and Demultiplexers

# 3.1 Objectives

- ✤ To understand the operating principles of Encoders/Decoders

- To understand the operating principles of Multiplexers/Demultiplexers

- ✤ To construct Encoders and Decoders using basic gates and ICs

- ✤ To construct Multiplexers and Demultiplexers using basic gates and ICs

# 3.2 Equipment Required

- ✤ IT-3000 Basic Electricity Circuit Lab

- ✤ IT-3004 Encoder/Decoder Circuits

- IT-3005 Multiplexer/Demultiplexer Circuits

# 3.3 Pre Lab

- 1) Using proteus build the following circuit and show why you use the components:

- a) Build 1x2 Decoder basic gates.

- b) Build the above circuit using universal gates.

- c) Build a 2x1 Encoder using basic gates.

- d) Build an 8x1 Multiplexer using basic gates.

- e) Build a 1x8 Demultiplexer using basic gates.

- f) Write truth table for all above circuits.

- 2) Design a circuit which uses an SN74151 to implement a sum-of-products expression, as follows:

- a) Convert the following expression into summation form (i.e., F (A, B, C) =  $\sum (...)$ ):

$$Y = f(A, B, C) = A\overline{B} + \overline{B}C$$

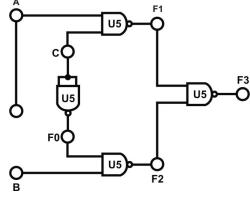

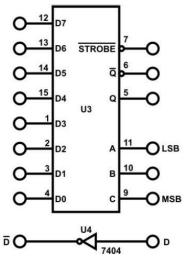

b) Sketch on Figure 1 the input connections necessary to implement the function in part (a). Observe that the inputs are connected to 0 or 1 depending on the value of the function for that min term.

**Important:** Please note that this way we can implement a 3-input function (A, B, C) using an 8-to-1 MUX. Later we will see how to implement a 4-input function (A, B, C, D) using an 8-to-1 MUX. For that we will need to inspect the additional input (say D) with the corresponding function value. The possible inputs to the MUX are 0, 1, D, D<sup>\*</sup>.

| ) • | - A2    | Q Y |

|-----|---------|-----|

| 3 • | — A1    |     |

| :   |         |     |

| •   | -D7 AB  | с   |

|     | — D6 AB | ē   |

|     | - DS AB |     |

|     | —D4 AB  | ē   |

|     | — DЗ Āв |     |

|     | - D2 ĀB | ē   |

|     | -D1 AB  | с   |

|     |         | ē   |

Figure (1): Half-Adder Functional Diagram.

# 3.4 Theory

#### 3.4.1 Decoder

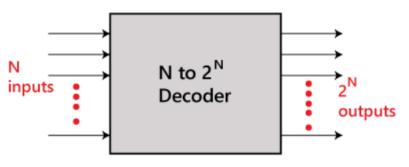

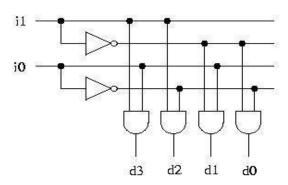

The combinational circuit that changes the binary information into  $2^N$  output lines is known as Decoders. The binary information is passed in the form of N input lines. The output lines define the  $2^N$ -bit code for the binary information. In simple words, the Decoder performs the reverse operation of the Encoder. At a time, only one input line is activated for simplicity. The produced  $2^N$ -bit output code is equivalent to the binary information. The outputs of the decoder are nothing, but the min terms of 'N' input variables lines as shown in figure 2.

Figure (2): General Decoder block diagram.

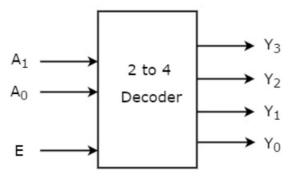

Example show 2 to 4 Decoder. Let 2 to 4 Decoder has two inputs A1 & A0 and four outputs Y3, Y2, Y1 & Y0. The block diagram of 2 to 4 decoder is shown in the following figure.

Figure (3): 2 to 4 Decoder with enable.

One of these four outputs will be '1' for each combination of inputs when enable, E is '1'. The Truth table of 2 to 4 decoder is shown below.

| Enable | Inp | outs |    | Out | puts |    |

|--------|-----|------|----|-----|------|----|

| Ε      | A1  | A0   | ¥3 | Y2  | Y1   | Y0 |

| 0      | X   | Х    | 0  | 0   | 0    | 0  |

| 1      | 0   | 0    | 0  | 0   | 0    | 1  |

| 1      | 0   | 1    | 0  | 0   | 1    | 0  |

| 1      | 1   | 0    | 0  | 1   | 0    | 0  |

| 1      | 1   | 1    | 1  | 0   | 0    | 0  |

| Table 1 | able 1 |

|---------|--------|

|---------|--------|

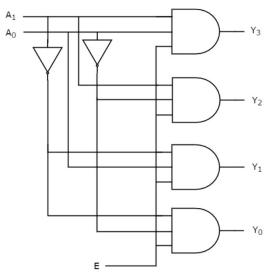

Each output is having one product term. So, there are four product terms in total. We can implement these four product terms by using four AND gates having three inputs each & two inverters. The circuit diagram of 2 to 4 decoder is shown in the following figure.

Figure (4): 2 to 4 Decoder circuit.

#### 3.4.2 Encoder

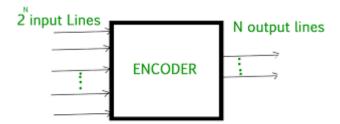

An Encoder is a combinational circuit that performs the reverse operation of Decoder. It has maximum of  $2^N$  input lines and 'N' output lines. It will produce a binary code equivalent to the input, which is active High. Therefore, the encoder encodes  $2^N$  input lines with 'n' bits. It is optional to represent the enable signal in encoders.

Figure (5): General encoder block diagram.

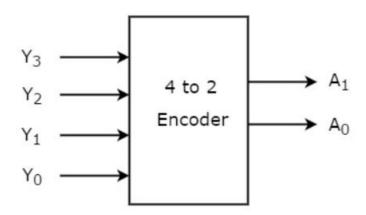

Example show 4 to 2 Encoder. Let 4 to 2 Encoder has four inputs Y3, Y2, Y1 & Y0 and two outputs A1 & A0. The block diagram of 4 to 2 Encoder is shown in the following figure.

Figure (6): 4 to 2 Encoder.

At any time, only one of these 4 inputs can be '1' to get the respective binary code at the output. The Truth table of 4 to 2 encoder is shown below.

|           | Out | puts |    | In | Inputs |  |  |

|-----------|-----|------|----|----|--------|--|--|

| <b>Y3</b> | Y2  | Y1   | YO | A1 | A0     |  |  |

| 0         | 0   | 0    | 1  | 0  | 0      |  |  |

| 0         | 0   | 1    | 0  | 0  | 1      |  |  |

| 0         | 1   | 0    | 0  | 1  | 0      |  |  |

| 1         | 0   | 0    | 0  | 1  | 1      |  |  |

| Table 2   |     |      |    |    |        |  |  |

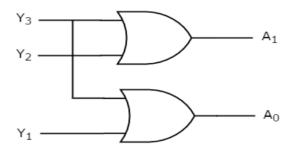

We can implement the above two Boolean functions by using two input OR gates. The circuit diagram of 4 to 2 encoder is shown in the following figure.

Figure (7): 2 to 4 Decoder circuit.

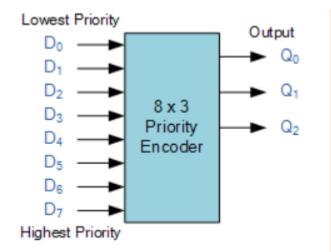

The Priority Encoder solves the problems mentioned above by allocating a priority level to each input. The priority encoders output corresponds to the currently active input which has the highest priority. So, when an input with a higher priority is present, all other inputs with a lower priority will be ignored.

The priority encoder comes in many different forms with an example of an 8-input priority encoder along with its truth table shown below.

(a) 8 to 3 priority Encoder block diagram.

|       |                |       | Inp   | uts   |       |       |                | 0              | utpu | uts |

|-------|----------------|-------|-------|-------|-------|-------|----------------|----------------|------|-----|

| $D_7$ | D <sub>6</sub> | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | D <sub>0</sub> | Q <sub>2</sub> | Q1   | Qo  |

| 0     | 0              | 0     | 0     | 0     | 0     | 0     | 1              | 0              | 0    | 0   |

| 0     | 0              | 0     | 0     | 0     | 0     | 1     | x              | 0              | 0    | 1   |

| 0     | 0              | 0     | 0     | 0     | 1     | x     | x              | 0              | 1    | 0   |

| 0     | 0              | 0     | 0     | 1     | х     | х     | x              | 0              | 1    | 1   |

| 0     | 0              | 0     | 1     | х     | х     | х     | x              | 1              | 0    | 0   |

| 0     | 0              | 1     | x     | х     | х     | x     | x              | 1              | 0    | 1   |

| 0     | 1              | х     | x     | x     | х     | x     | x              | 1              | 1    | 0   |

| 1     | x              | x     | x     | x     | х     | x     | x              | 1              | 1    | 1   |

Figure (8): 8 to 3 priority Encoder.

#### 3.4.3 Multiplexer

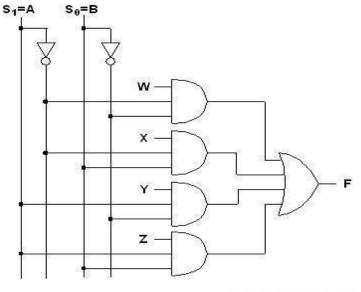

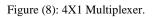

Multiplexer is a combinational circuit that has maximum of  $2^n$  data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines. Since there are 'n' selection lines, there will be  $2^n$  possible combinations of zeros and ones. So, each combination will select only one data input. Multiplexer is also called as Mux.

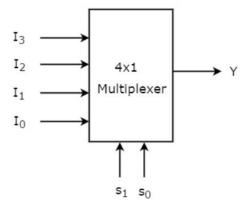

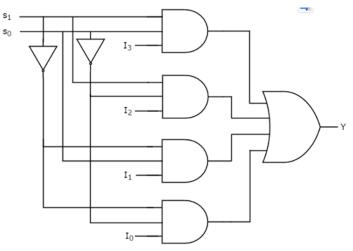

Example show 4 to 1 Mux. 4x1 Multiplexer has four data inputs I3, I2, I1 & I0, two Page | 47 selection lines s1 & s0 and one output Y. The block diagram of 4x1 Multiplexer is shown in the following figure.

Figure (9): 4 to 1 Mux block diagram.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. Truth table of 4x1 Multiplexer is shown below.

| Selec     | tions     | Outputs        |

|-----------|-----------|----------------|

| <b>S1</b> | <b>S2</b> | Y              |

| 0         | 0         | Io             |

| 0         | 1         | I <sub>1</sub> |

| 0         | 0         | I <sub>2</sub> |

| 1         | 1         | I <sub>3</sub> |

|           |           |                |

| Table | 3 |

|-------|---|

|-------|---|

We can implement this Boolean function using Inverters, AND gates & OR gate. The circuit diagram of 4x1 multiplexer is shown in the following figure.

Figure (10): 4 to 1 multiplexer circuit.

#### 3.4.4 De-Multiplexer

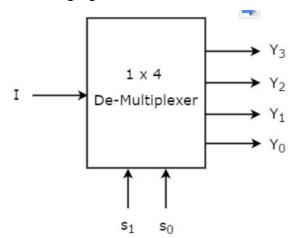

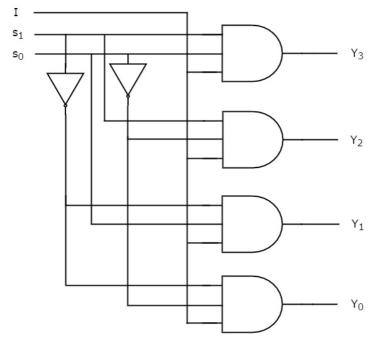

De-Multiplexer is a combinational circuit that performs the reverse operation of Multiplexer. It has single input, 'n' selection lines and maximum of  $2^n$  outputs. The input will be connected to one of these outputs based on the values of selection lines. Since there are 'n' selection lines, there will be  $2^n$  possible combinations of zeros and ones. So, each combination can select only one output. De-Multiplexer is also called as De-Mux.

Example show 1x4 De-Multiplexer. 1x4 De-Multiplexer has one input I, two selection lines, s1 & s0 and four outputs Y3, Y2, Y1 &Y0. The block diagram of 1x4 De-Multiplexer is shown in the following figure.

Figure (9): 1 to 4 De-Mux block diagram.

The single input 'I' will be connected to one of the four outputs, Y3 to Y0 based on the values of selection lines s1 & s0. The Truth table of 1x4 De-Multiplexer is shown below.

| Selec | ctions | Outputs |    |    |    |  |  |  |  |

|-------|--------|---------|----|----|----|--|--|--|--|

| S1    | S2     | ¥3      | Y2 | Y1 | Y0 |  |  |  |  |

| 0     | 0      | 0       | 0  | 0  | Ι  |  |  |  |  |

| 0     | 1      | 0       | 0  | Ι  | 0  |  |  |  |  |

| 0     | 0      | 0       | Ι  | 0  | 0  |  |  |  |  |

| 1     | 1      | Ι       | 0  | 0  | 0  |  |  |  |  |

We can implement these Boolean functions using Inverters & 3-input AND gates. The circuit diagram of 1x4 De-Multiplexer is shown in the following figure.

Figure (10):1 to 4 De-multiplexer circuit.

# 3.5 Procedure

#### **3.5.1** Constructing a 4-to-2 Encoder with Basic Gates

Constructing a 4-to-2 Encoder with Basic Gates (Module IT-3004 block Encoder 1).

1. Insert connection clips according to Figure 11.

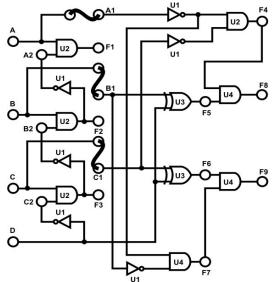

Figure (11): wiring diagram of 4-to-2-line Encoder.

2. Connect +5V of module IT-3004 to the +5V output of fixed power supply section of IT-3000.

3.Connect inputs A~D to Date Switches SW0~SW3 respectively; outputs F8 and F9 to Logic Indicator L0 and L1.

4.Follow the input sequences for D, C, B, A; in Table 5 and record the output states.

| D | С | В | Α | <b>F9</b> | F8 |

|---|---|---|---|-----------|----|

| 0 | 0 | 0 | 0 |           |    |

| 0 | 0 | 0 | 1 |           |    |

| 0 | 0 | 1 | 0 |           |    |

| 0 | 0 | 1 | 1 |           |    |

| 0 | 1 | 0 | 0 |           |    |

| 0 | 1 | 0 | 1 |           |    |

| 0 | 1 | 1 | 0 |           |    |

| 0 | 1 | 1 | 1 |           |    |

| 1 | 0 | 0 | 0 |           |    |

| 1 | 0 | 0 | 1 |           |    |

| 1 | 0 | 1 | 0 |           |    |

| 1 | 0 | 1 | 1 |           |    |

| 1 | 1 | 0 | 0 |           |    |

| 1 | 1 | 0 | 1       |  |

|---|---|---|---------|--|

| 1 | 1 | 1 | 0       |  |

| 1 | 1 | 1 | 1       |  |

|   |   |   | Table 5 |  |

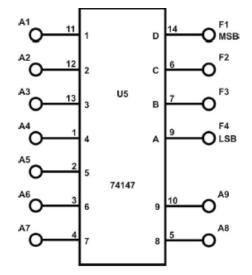

#### 3.5.2 Constructing 9-to-4-Line Encoder with TTL IC

The 74147 (U5) on block Encoder 2 of module IT-3004 is used in this section of the experiment. Connect +5V of module IT-3004 to the +5V output of fixed power supply. Note that the IC uses only 9 inputs.

Figure (12): 74147 BCD Priority Encoder.

2. As you know, the main kit has 2 sets of DIP switches, with 8 switches each: 1.1-1.8 and 2.1-2.8. Connect inputs A1~A8 to DIP Switches 1.1~1.8 and A9 to 2.1 (or one of the unused main switches S1-S4). Connect outputs F1~F4 to Logic indicators L1~L4. Follow the input sequences given in Table 6 and record output states. Be aware of the active LOW and active HIGH polarity for the inputs/outputs when interpreting the results.

| A9 | <b>A8</b> | A7 | A6 | A5 | A4 | A3 | A2 | A1 | F4 | F3 | F2 | F1 |

|----|-----------|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 1         | 1  | 1  | 1  | 1  | 1  | 1  | 1  |    |    |    |    |

| 0  | 0         | 1  | 1  | 1  | 1  | 1  | 1  | 1  |    |    |    |    |

| 1 | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 0 |  |  |  |

|---|---------|---|---|---|---|---|---|---|--|--|--|

| 1 | 1       | 1 | 1 | 1 | 1 | 1 | 0 | 0 |  |  |  |

| 1 | 1       | 1 | 1 | 1 | 1 | 0 | 1 | 1 |  |  |  |

| 1 | 1       | 1 | 1 | 1 | 0 | 0 | 0 | 0 |  |  |  |

| 1 | 1       | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |  |  |

| 1 | 1       | 1 | 1 | 0 | 0 | 0 | 1 | 1 |  |  |  |

| 1 | 1       | 1 | 0 | 1 | 1 | 1 | 0 | 0 |  |  |  |

| 1 | 1       | 0 | 1 | 1 | 0 | 1 | 1 | 0 |  |  |  |

| 1 | 1       | 0 | 0 | 0 | 1 | 1 | 1 | 1 |  |  |  |

| 1 | 0       | 0 | 0 | 0 | 1 | 1 | 1 | 1 |  |  |  |

|   | Table 6 |   |   |   |   |   |   |   |  |  |  |

#### 3.5.3 Constructing 2-to-4 Line Decoder with Basic Gates

Block Decoder 1 of module IT-3004 will be used in this section of the experiment. Connect +5V of module IT-3004 to the +5V output of fixed power supply.

Figure (13): 2-to-4 Decoder.

- Connect inputs A, B to Data Switches SW0 and SW1. Connect outputs F1~F4 to Logic Indicators L0~L3 respectively.

- 3. Follow the input sequences for A and B in Table 7 and record output states.

| В | Α       | F1 | F2 | F3 | F4 |  |  |  |  |

|---|---------|----|----|----|----|--|--|--|--|

| 0 | 0       |    |    |    |    |  |  |  |  |

| 0 | 1       |    |    |    |    |  |  |  |  |

| 1 | 0       |    |    |    |    |  |  |  |  |

| 1 | 1       |    |    |    |    |  |  |  |  |

|   | Table 7 |    |    |    |    |  |  |  |  |

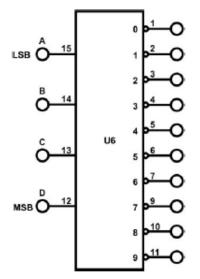

#### 3.5.4 Constructing 4-to-10 Line Decoder with TTL IC

U6 (7442) on block Decoder 2 of module IT-3004 will be used in this section of the experiment. 7442 is a BCD-to-Decimal decoder IC. BCD: Binary Coded Decimal.

Figure (14): 4-to-10-line Decoder.

- 2. Connect inputs A, B, C and D to the Data Switches SW0, SW1, SW2 and SW3, respectively. Connect 10 outputs to corresponding Indicators L0~L9.

- Adjust the switches according to Table 2.2. Observe the output states at L0~L9. Record input and output logic states in Table 8. (Note input is the binary number for number in first column).

|   |   | In | out |   |   |   |   |   | Out | tput |   |   |   |   |

|---|---|----|-----|---|---|---|---|---|-----|------|---|---|---|---|

|   | D | С  | В   | Α | 0 | 1 | 2 | 3 | 4   | 5    | 6 | 7 | 8 | 9 |

| 0 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 1 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 2 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 3 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 4 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 5 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 6 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 7 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 8 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

| 9 |   |    |     |   |   |   |   |   |     |      |   |   |   |   |

Table 8

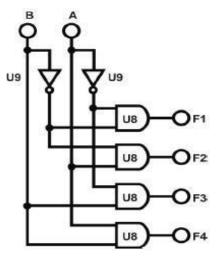

#### 3.5.5 Constructing 2-to-1-Line Multiplexer with basic Gates

1. Block Multiplexer 1 of module IT-3005 will be used as a 2-to-1 MUX. Connect

+5V of module IT-3005 to the +5V output of fixed power supply.

Figure (15): 2-to-1 Multiplexer.

- Connect inputs A, B to Data Switches SW0, SW1; Selector C to SW2. Connect output F3 to Logic Indicator L0.

- 3. Follow the input sequences in Table 3.5 and record states of F3. Which input (A or B) determines the output for each value of C? Does this correspond to a 2-to-1 Multiplexer as you know it?

| 0       | 0 | 1 |  |  |  |  |  |

|---------|---|---|--|--|--|--|--|

| 0       | 1 | 0 |  |  |  |  |  |

| 0       | 1 | 1 |  |  |  |  |  |

| 1       | 0 | 0 |  |  |  |  |  |

| 1       | 0 | 1 |  |  |  |  |  |

| 1       | 1 | 0 |  |  |  |  |  |

| 1       | 1 | 1 |  |  |  |  |  |

| Table 9 |   |   |  |  |  |  |  |

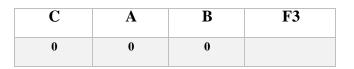

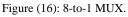

#### 3.5.6 Constructing 8-to-1 Line Multiplexer with IC

1. Block Multiplexer 1 of module IT-3005 will be used as a 2-to-1 MUX. Connect

+5V of module IT-3005 to the +5V output of fixed power supply.

2. Refer to the data sheet for specifications of the 74LS151. A, B, C are the control (selection) inputs: CBA is the value of C then B then A. So, CBA=011 means that C=0, B=1, A=1. Q is the output of the MUX.

When CBA = "000", data at D0 is send to output Q.

When CBA = "010", data at D2 is send to output Q.

:

When CBA = "111", data at D7 is send to output Q.

The IC will function properly only when STROBE = "0".

When STROBE = "1" IC do not change output according to inputs, Q will remain "1".

Connect inputs D0~D7 to DIP Switch 1.0~1.7; inputs C, B, A to Data Switches SW2, SW1, SW0. Follow the input sequences in Table 6, adjust D0~D7 and CBA and record output states. Determine which input among D0~D7 does Q depend on.

| С | Α        | B | Q |  |  |  |  |  |  |

|---|----------|---|---|--|--|--|--|--|--|

| 0 | 0        | 0 |   |  |  |  |  |  |  |

| 0 | 0        | 1 |   |  |  |  |  |  |  |

| 0 | 1        | 0 |   |  |  |  |  |  |  |

| 0 | 1        | 1 |   |  |  |  |  |  |  |

| 1 | 0        | 0 |   |  |  |  |  |  |  |

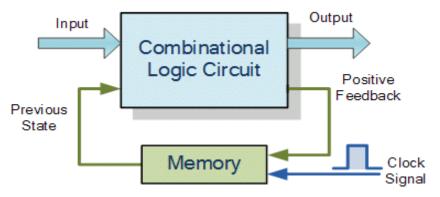

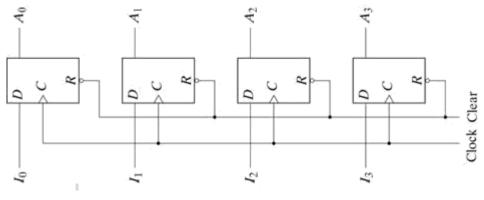

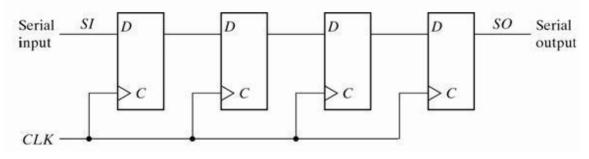

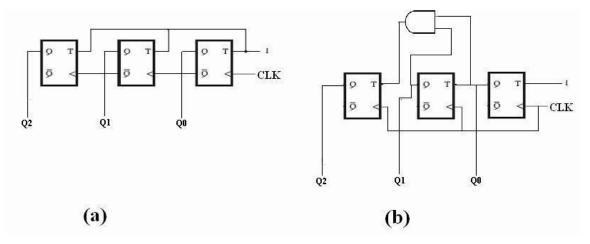

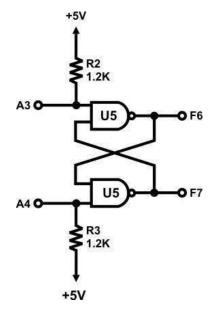

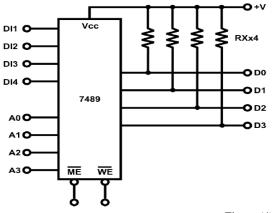

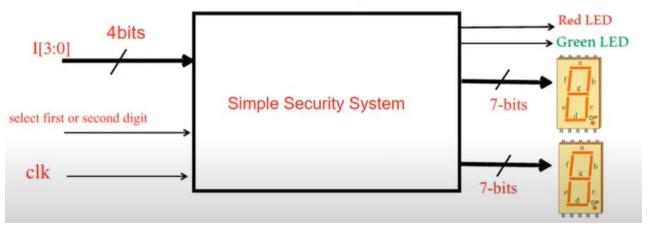

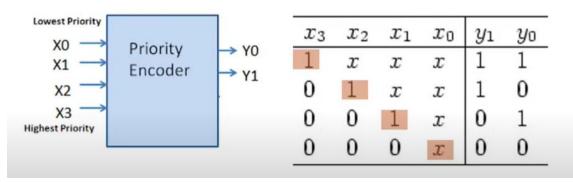

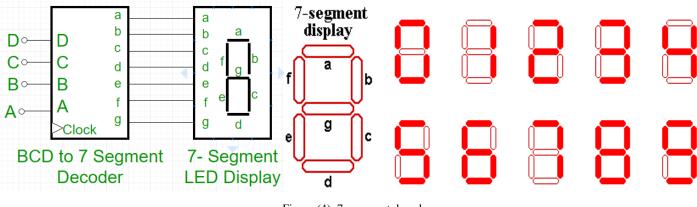

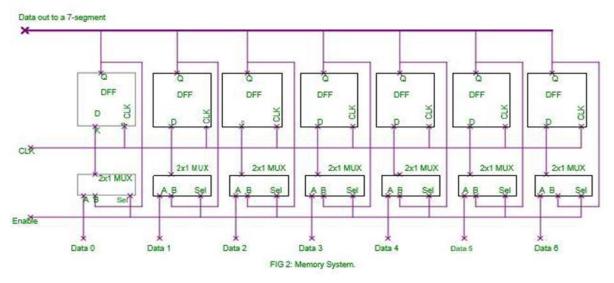

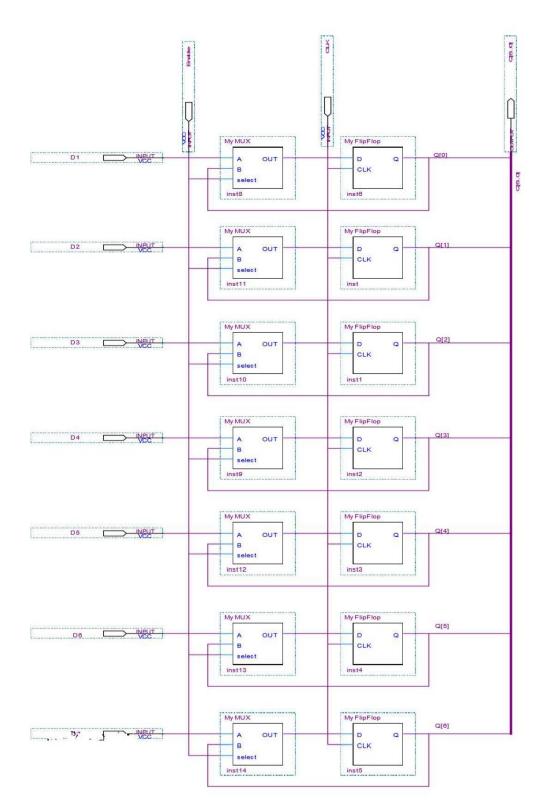

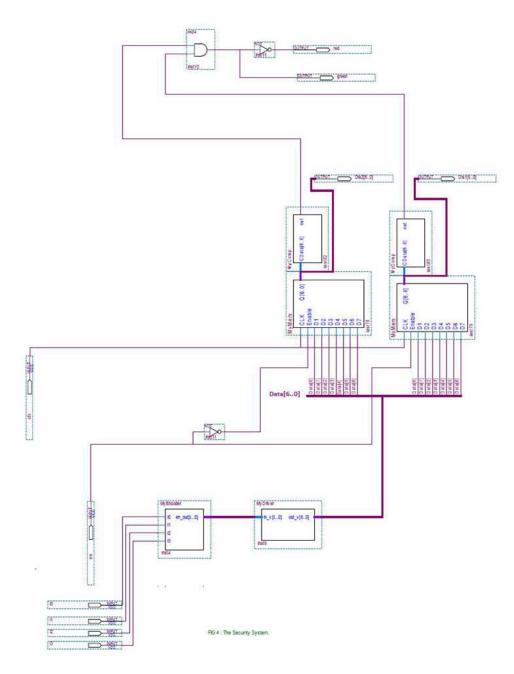

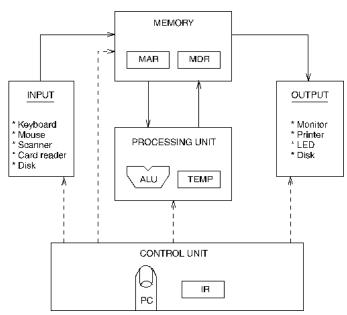

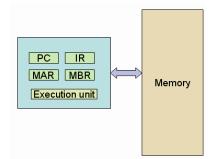

| 1 | 0        | 1 |   |  |  |  |  |  |  |